# Burn-in & Test Socket Workshop

March 6-9, 2005 Hilton Phoenix East / Mesa Hotel Mesa, Arizona

ARCHIVE

# **COPYRIGHT NOTICE**

- The papers in this publication comprise the proceedings of the 2005 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

- There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

- The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

## **Technical Program**

#### BiTS Tutorial Sunday 3/06/05 1:00PM

#### "Signal Integrity of Sockets – Simplified!"

Eric Bogatin Chief Technical Officer Synergetix

# **Signal Integrity of Sockets- Simplified!**

Dr. Eric Bogatin CTO, Synergetix Kansas City, KS eric@idinet.com

2005 Burn-in and Test Socket Workshop March 6 - 9, 2005

Burn-in & Test Socket Workshop

- ✓ Who cares?

- ✓ What's important: signal integrity, power integrity

- ✓ Common vocabulary

- ✓ Insertion loss: what is and is not important?

- ✓ Loop inductance: what is and is not important?

# *"It is better to uncover a little than to cover a lot" - Francis Low*

#### Electrical Performance in Perspective

- Performance

- ✓ Compliance

- ✓ Pitch

- ✓ Cycle lifetime

- ✓ Time between cleaning

- ✓ Electrical

- DC resistance

- Hi Frequency

- Signal Integrity

- » Bandwidth

- » Insertion loss

- » Return loss

- » SPICE models

- Power integrity

- » Loop inductance

**Constraints:**

- Vendors

- Corporate Culture

- Compatibility: Industry, Legacy

Cost: \$\$\$, TCOO, Schedule, Risk

**Partitioning:**

- Pin electronics

- Wiring/cabling

- Loadboards

- Sockets

© Eric Bogatin 2005

М

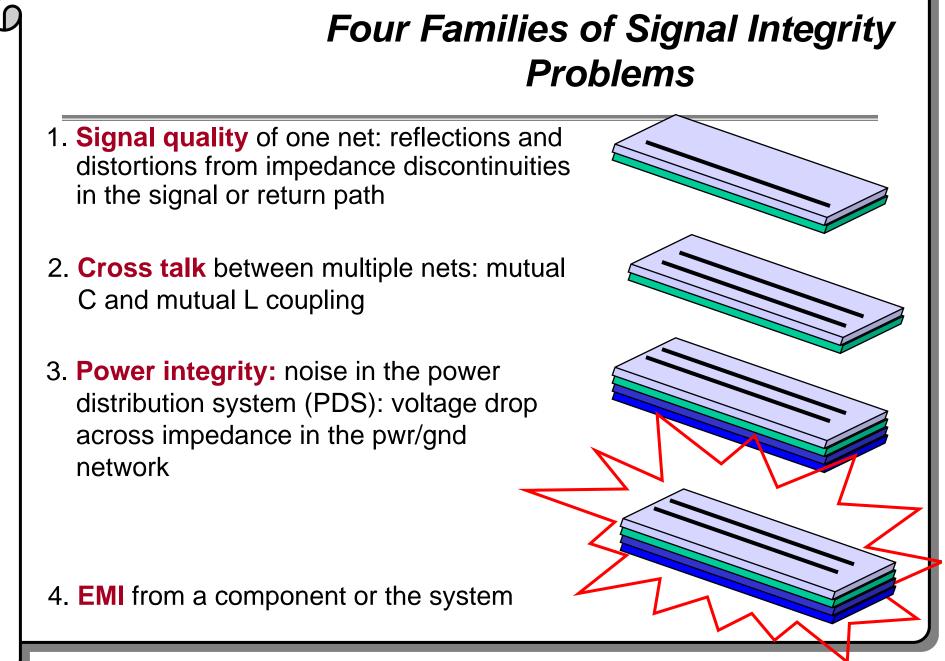

## Signal Integrity Problems

| TERMINATIONS       | LINE DE                    | LAY                  | PARASITICS | \$   | CAPACITANCE             |

|--------------------|----------------------------|----------------------|------------|------|-------------------------|

| EMISSIONS          | GROUN                      | D BOUNCE             | EMI/EN     | -    | LOADED LINES            |

| ATTENUATION        | F                          | POWER AND            |            |      |                         |

| NON-MONOTONIC EDGE |                            | ND DISTRIBU          |            | ΓURN | LOSS                    |

| GROUND BOUNCE      | GROU                       |                      | TION       | CRI  | TICAL NET               |

| SKIN DEPTH         |                            | SUSCEPTA<br>DUCTANCE |            |      | AL INTEGRITY<br>IR DROP |

| INDUCTANCE         |                            |                      |            |      |                         |

| INSERTION LOSS     | RINGING                    | <b>RISE TIME</b>     | DEGRADATIC | ON ( | CROSSTALK               |

|                    | <b>RETURN CURRENT PATH</b> |                      |            | STUE | LENGTHS                 |

| MODE CONVERSION    |                            |                      |            |      | N PLANES                |

| TRANSMISSION LINES | IMPEDA                     | NCE DISCON           |            |      |                         |

|                    | DELTA I NOISE              |                      |            |      | CTIONS                  |

| UNDERSHOOT, OVERSI | HOOT                       | RC DEL               | <b>Α</b> Υ |      | DISPERSION              |

|                    |                            |                      |            |      |                         |

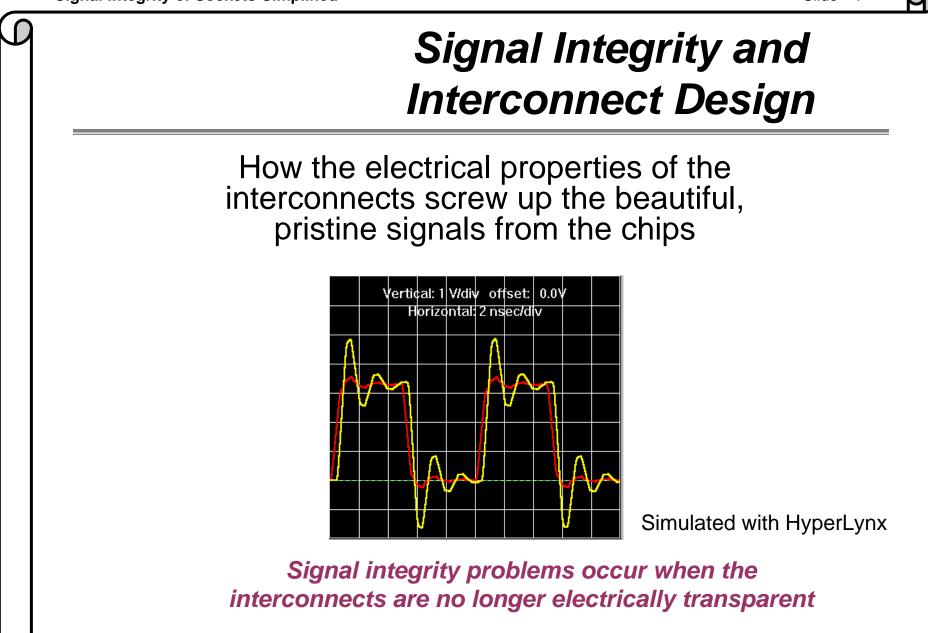

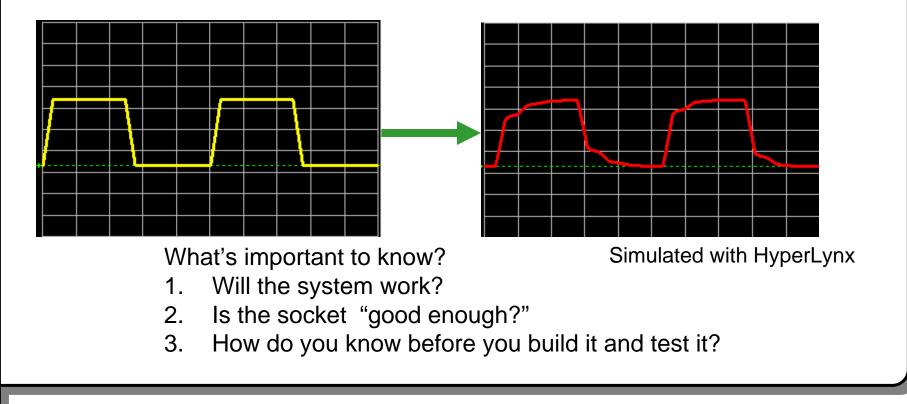

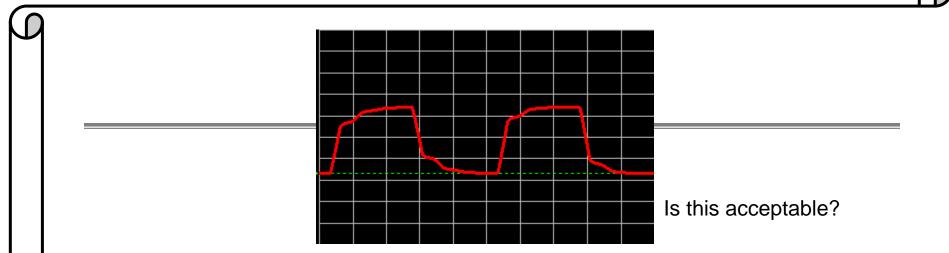

Purpose of an interconnect: "to transport a signal from one point to another with an acceptable level of distortion"

- Good news:

- ✓ Always the final test

- ✓ 100% certainty for that situation

#### Bad news

- ✓ What about the next socket?

- ✓ What do you tell your supplier?

- ✓ How does supplier evaluate quality?

- ✓ If it doesn't work, where do you look to re-design?

- ✓ Can you afford the time for multiple iterations?

- "Build it and test it" works when the interconnects are electrically transparent

- ✓ Other specification methods are required for f > ~ 500 MHz

- ✓ Everything except "build it and test it" is a compromise

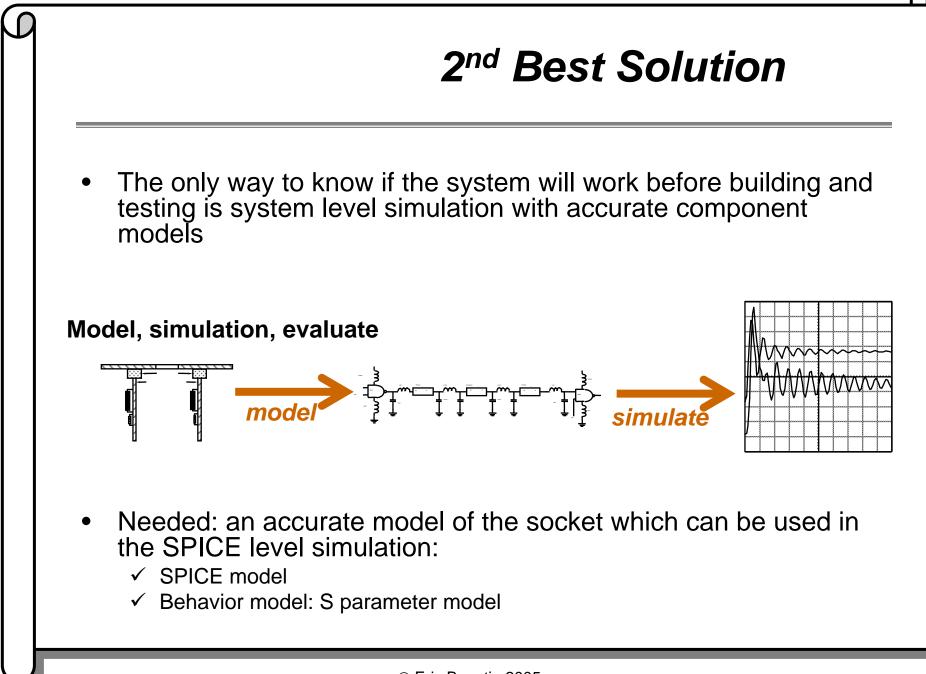

## 3<sup>rd</sup> Best Alternative

- Specify values of model parameters

- $\sim Z_0$

- ✓ TD

- ✓ L

- ✓ C

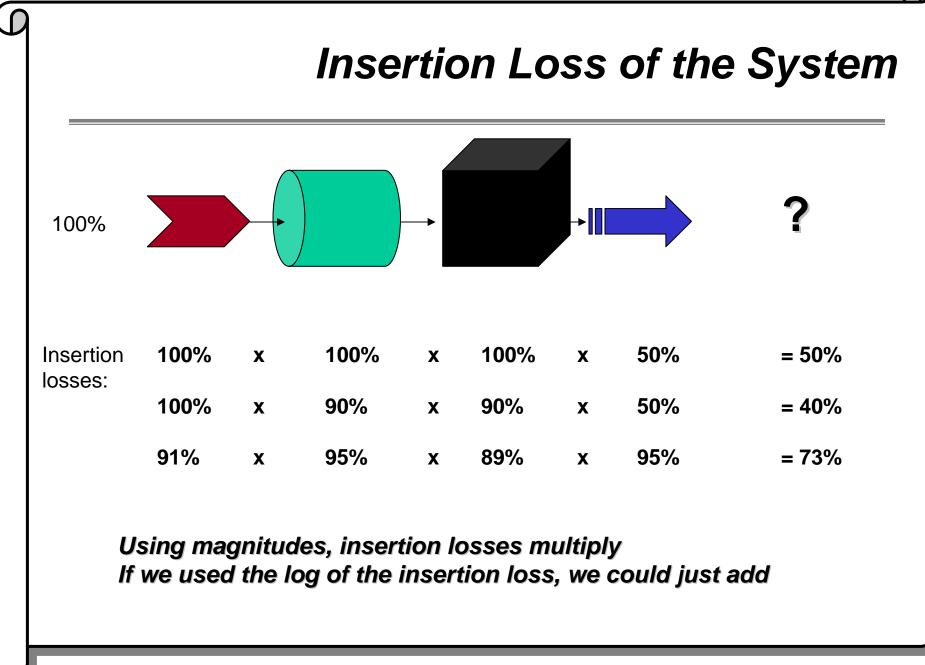

- Insertion loss

- ✓ Return loss

- Specifications based on *assumptions* of the rest of the system

- Specifications are a pre-arranged compromise- sometimes based on:

- ✓ System level simulation balancing cost-performance-constraints- (really hard!)

- ✓ A guess

- ✓ Because it worked in the last design

- $\checkmark$  Enough margin for designer to sleep at night

- ✓ Assuming performance is free

- ✓ Incorrect assumptions

- Information that was passed from engineer to engineer to engineer to engineer...(only one of whom might have an idea of what they want)

H)

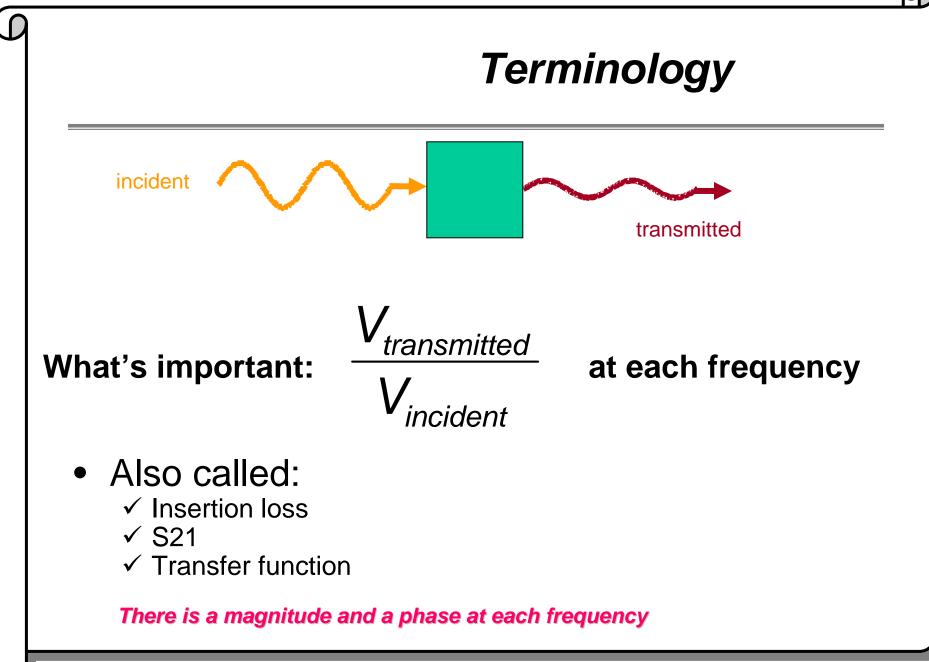

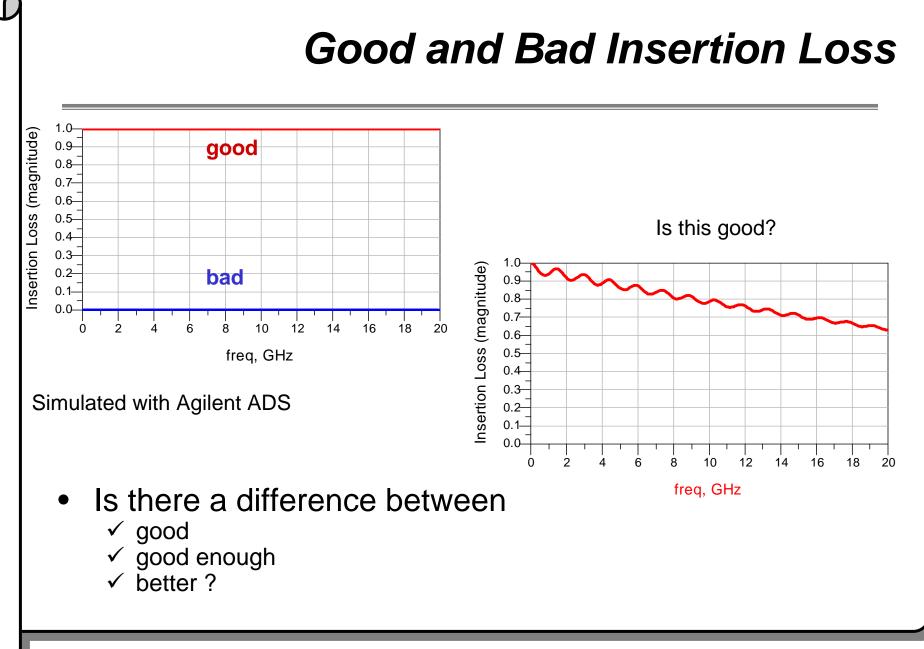

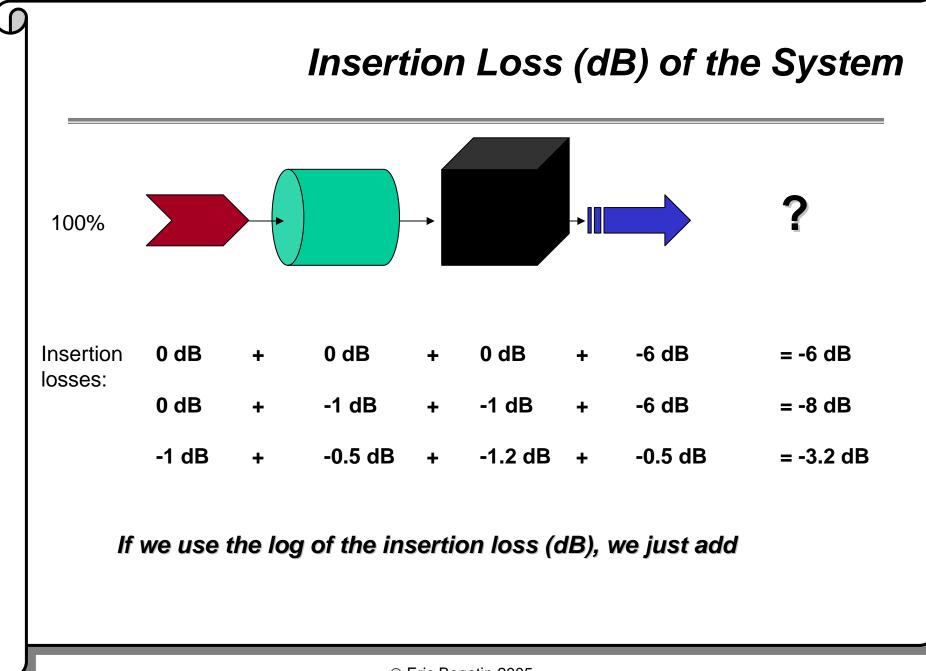

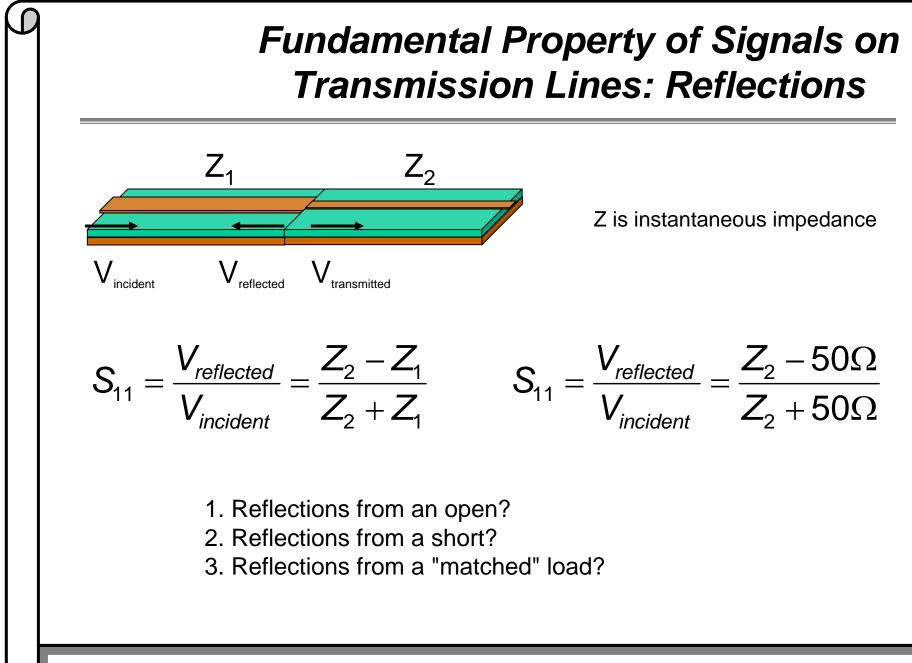

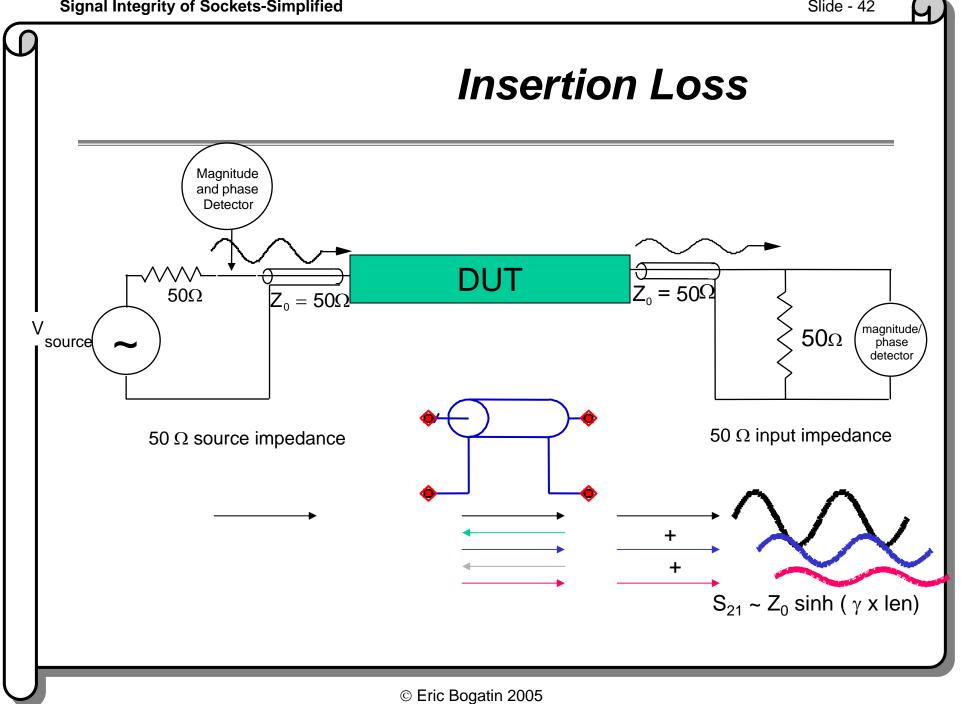

Universally used metric to define "goodness" of a socket:

#### -1 dB insertion loss bandwidth

- Bandwidth

- Insertion loss

- dB

- Why -1 dB

- What design features influence this performance

Slide - 12

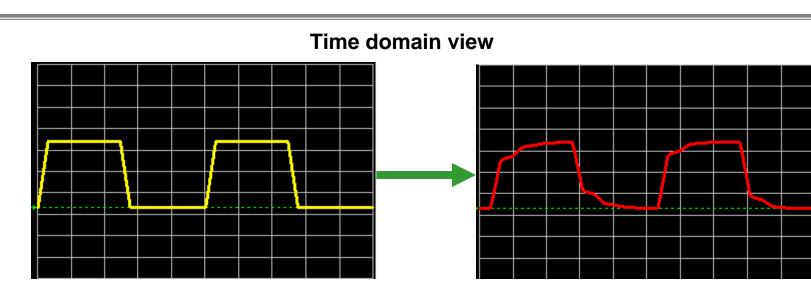

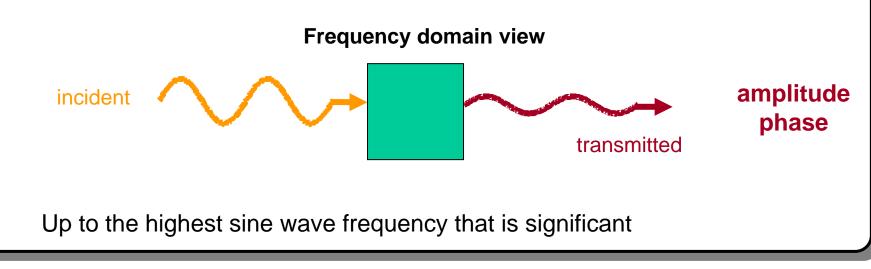

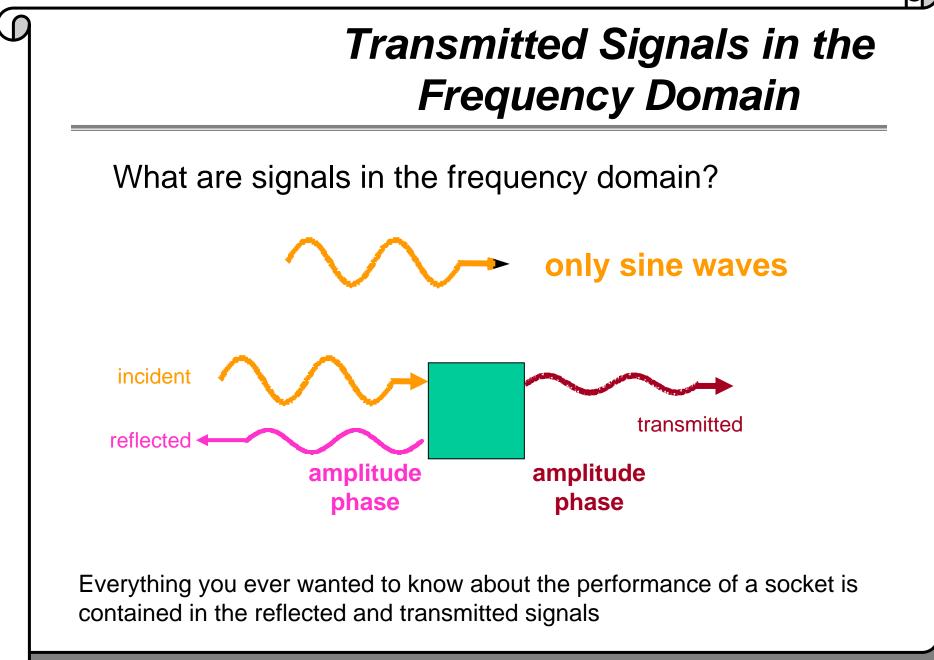

# Sometimes the frequency domain offers an easier path to the answer

No new information in the frequency domain

The only reason we'd ever leave the time domain to go to the frequency domain:

To get to the answer faster.

© Eric Bogatin 2005

# Bandwidth: the highest sine wave frequency that is *significant*

<sup>©</sup> Eric Bogatin 2005

Slide - 16

## Clock Frequency and Bandwidth

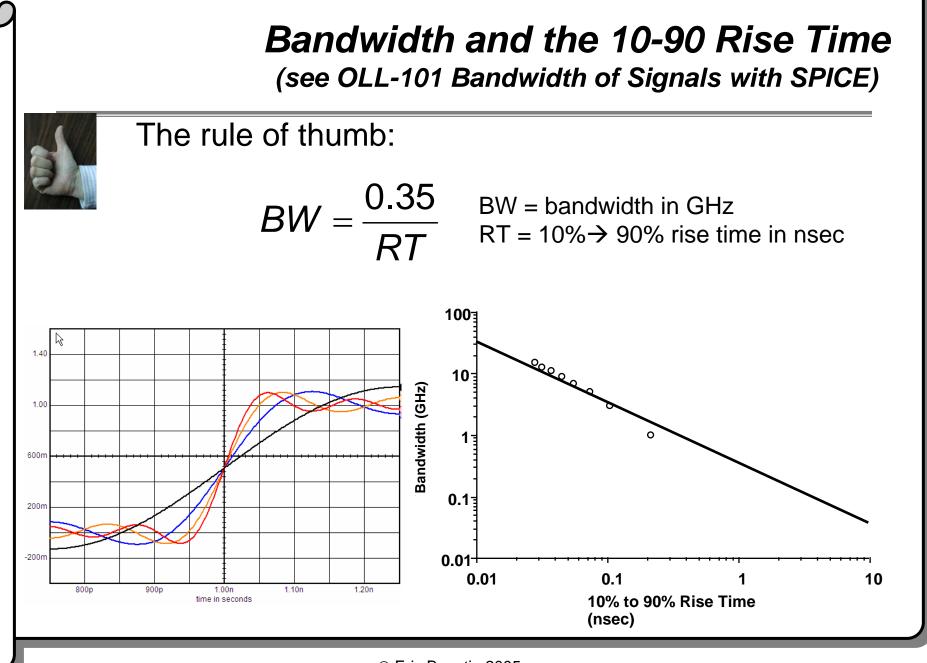

$RT \approx 7 \% T$  (a little aggressive, i.e., conservative estimate)

$$T_{period} = 15 \text{ x RT}$$

$RT = \frac{0.35}{BW}$

$$T_{period} = 15 \frac{0.35}{BW} \approx \frac{5}{BW}$$

$T_{period} = \frac{1}{F_{clock}}$

If you don't know the rise time: BW = 5 x F<sub>clock</sub> As a rough rule of thumb

# Bandwidth and Bit Rate in high speed serial links ( > 2 Gbps)

$\mathbf{O}$ Utilities Help 5000 Waveforms 🗁 🛠 🍂 👯 C 🛛 Run/Stop Acq Mode Sample 💽 Trig External Direct 💿 🦯 0.0V Pulse 💌 Amplitude 💌 fift nun Lift AA TITL 100 1200 AA 🗡 🏊 🌞 🌺 🕼 100 💳 🔨 🎞 🔺 🕱 M1 100.3mV/div /mDB M1 122.0ps 63.5% 99.3% 100.0% 1620 me 4998 M1 ▲ 100.3mV/ 🛛 🛨 0.0V 🗑 🛫 Main 🔍 🔍 100.000ps 🗒 🛫 21.500n 8:30 AM 3/12/04

3,125 Gbps, Altera Stratix GX driver signal, after 42 inches on FR4 courtesy of Altera

BR = bit rate BW = bandwidth

For most high speed serial links: Repeat frequency =  $\frac{1}{2} \times BR$ (for the 1010101010 pattern)

- For the highest BR high speed serial links:

- $\checkmark\,$  signal is almost a sine wave

- BW ~ 1st harmonic of the repeat frequency

- ✓ BW = ½ BR

The rule of thumb: BW ~ 1/2 x BR

- Bandwidth is the highest sine wave frequency component that is significant

- Bandwidth is inherently only a rough approximate term- if an accurate frequency value is important, can't use the bandwidth

- If the socket meets performance spec for frequencies up to the bandwidth, it is "good enough"

Slide - 19

Slide - 23

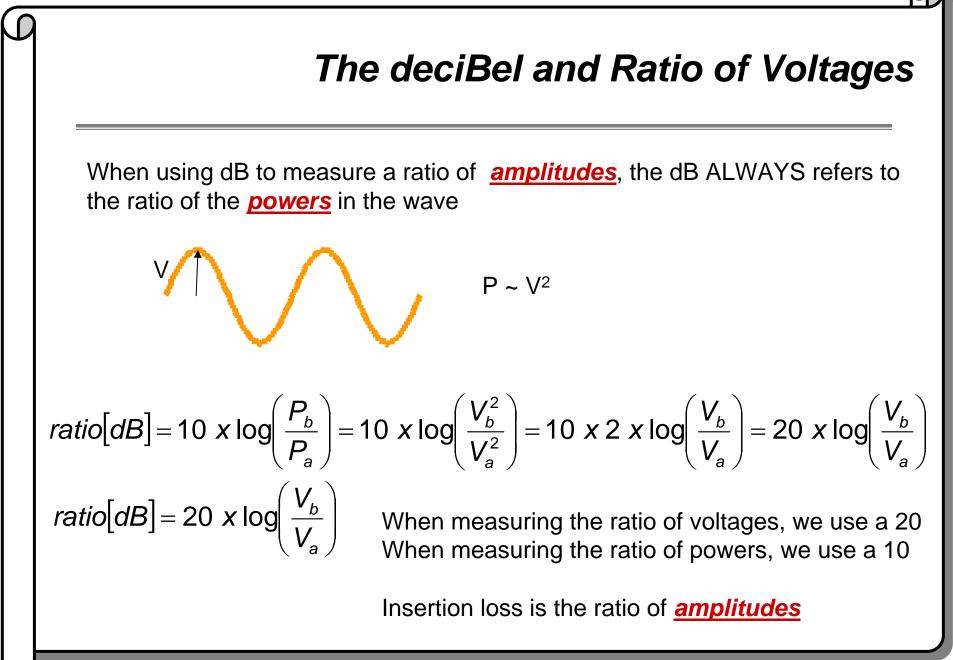

#### The deciBel and Powers

Formalism: log of the ratio of two powers is in Bels

$ratio[Bels] = \log\!\left(\frac{P_b}{P_a}\right)$

10 deciBel = 1 Bels

$ratio[dB] = 10 \ x \log\left(\frac{P_b}{P_a}\right)$

$\frac{0.1 \, watt}{1 \, watt} = 10^{-1} = -10 \, dB$

$\frac{0.001 \, watt}{1 \, watt} = 10^{-3} = -30 \, dB$

$$\frac{0.000001 \text{ watt}}{1 \text{ watt}} = 10^{-6} = -60 \text{ dB}$$

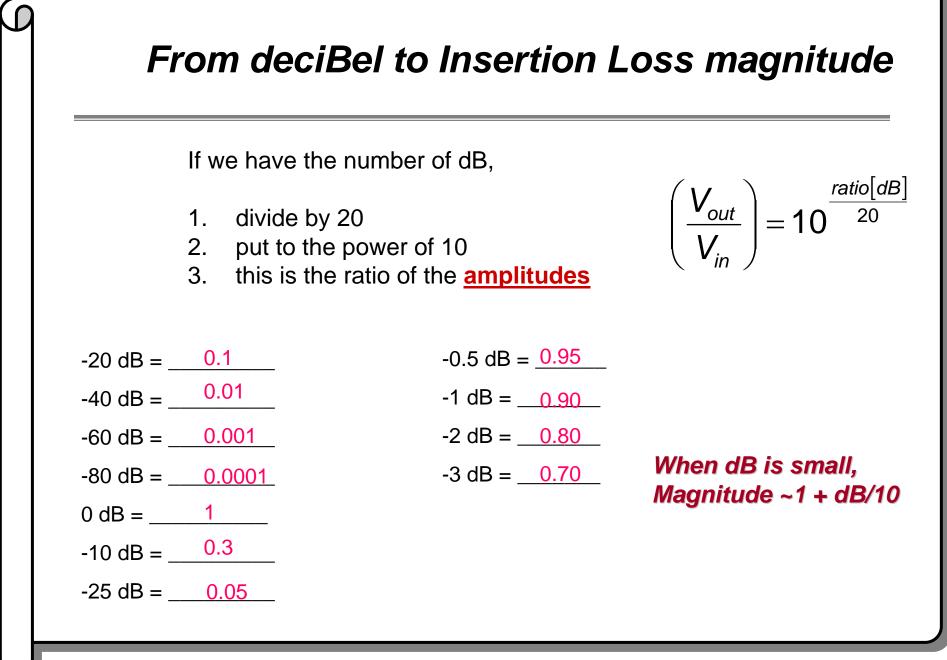

If we have the ratio of the **powers**, take the exponent of the power 10 and multiple by 10 to get the dB

If we have the number of dB, divide by 10 and put to the power of 10 and this is the ratio of the **powers**

-10 dB = 0.1 -20 dB = 0.01 -40 dB = 0.01%

© Eric Bogatin 2005

μ

## From magnitude to dB

| If we have the ratio of the ampli                                                                                              | tudes,                                                       |                                                      |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|

| <ol> <li>Write it to the power of</li> <li>Take the exponent (or to</li> <li>Multiply by 20</li> <li>This is the dB</li> </ol> | $ratio[dB] = 20 \ x \log\left(\frac{V_{out}}{V_{in}}\right)$ |                                                      |

|                                                                                                                                | 10% = <u>-20 dB</u><br>1% = <u>-40 dB</u>                    |                                                      |

| $\frac{0.1  volt}{1  volt} = 10^{-1} = -20  dB$                                                                                | 0.001 = <u>-60 dB</u>                                        |                                                      |

| $\frac{0.01  volt}{1  volt} = 10^{-2} = -40  dB$                                                                               | 90% = -1 dB<br>80% = -2 dB<br>98% = -0.2 dB                  | When magnitude is close to 1,<br>dB ~ (mag – 1) x 10 |

|                                                                                                                                |                                                              |                                                      |

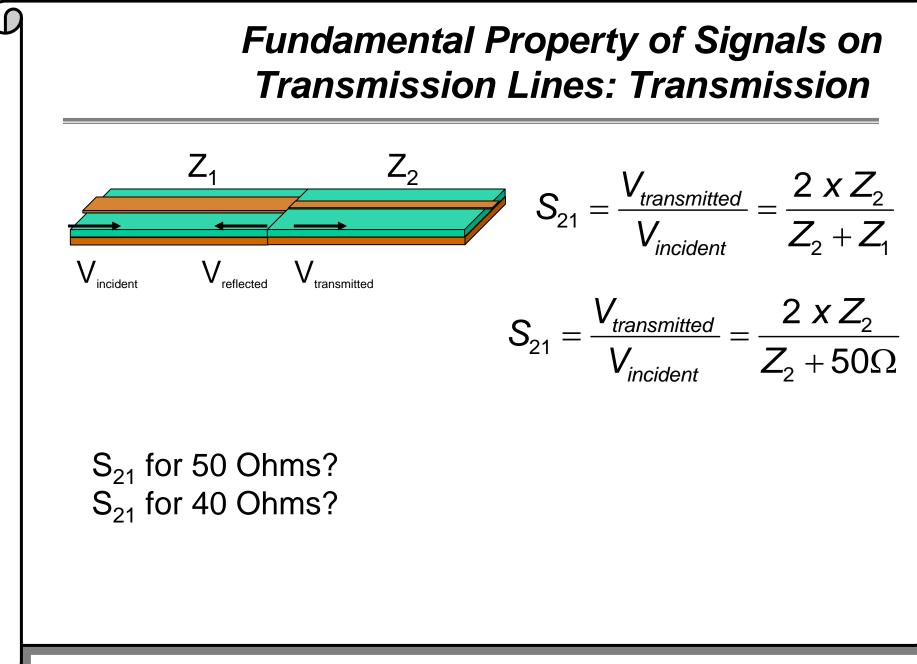

- All the signal transmits:  $S_{21} = 1 = 10^0 = 0 \text{ dB}$

- ✓  $S_{21} = 0$  dB everything is transmitted

- ✓ Transparent interconnect

- Very little signal transmits:  $S_{21} = 0.0001 = 10^{-4} = -80 \text{ dB}$

- ✓  $S_{21}$  = really big, negative number, no signal at the far end

- ✓ Really poor interconnect

#### Value of -1 dB Insertion Loss Bandwidth as a Metric

- Relative comparison

- First pass screening

- Rough, rule of thumb for usable operating frequency

- Should not be used to sign off on a design

- ✓ too approximate

- ✓ too much margin? Too little?

- ✓ Too many assumptions

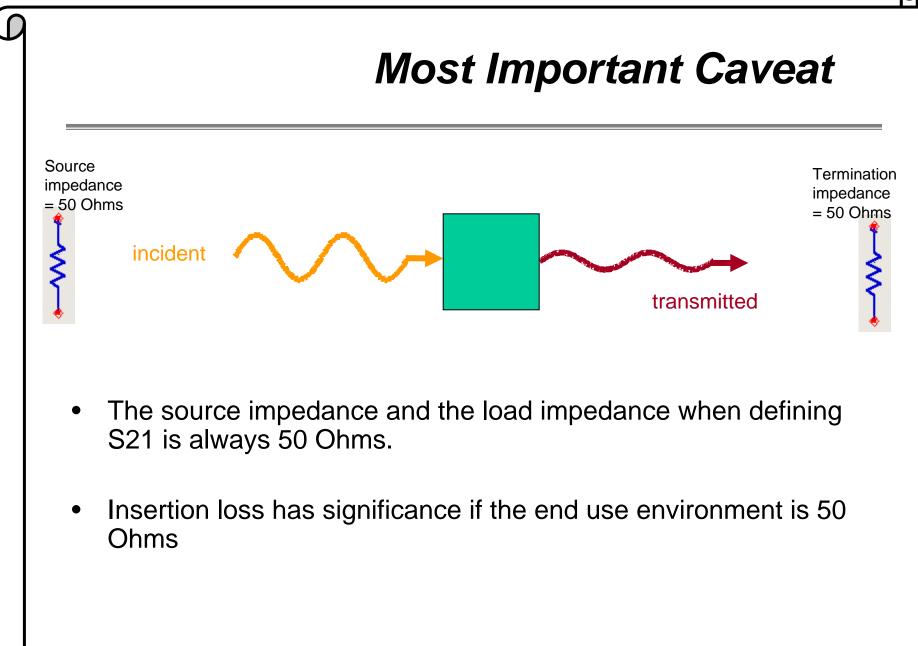

- Multiple approximations:

- ✓ Bandwidth of the signal

- ✓ Is the system a 50 Ohm system?

- ✓ Total system budget

- ✓ Allocation to the socket

- A better approach (and much more expensive):

- ✓ Model and simulate

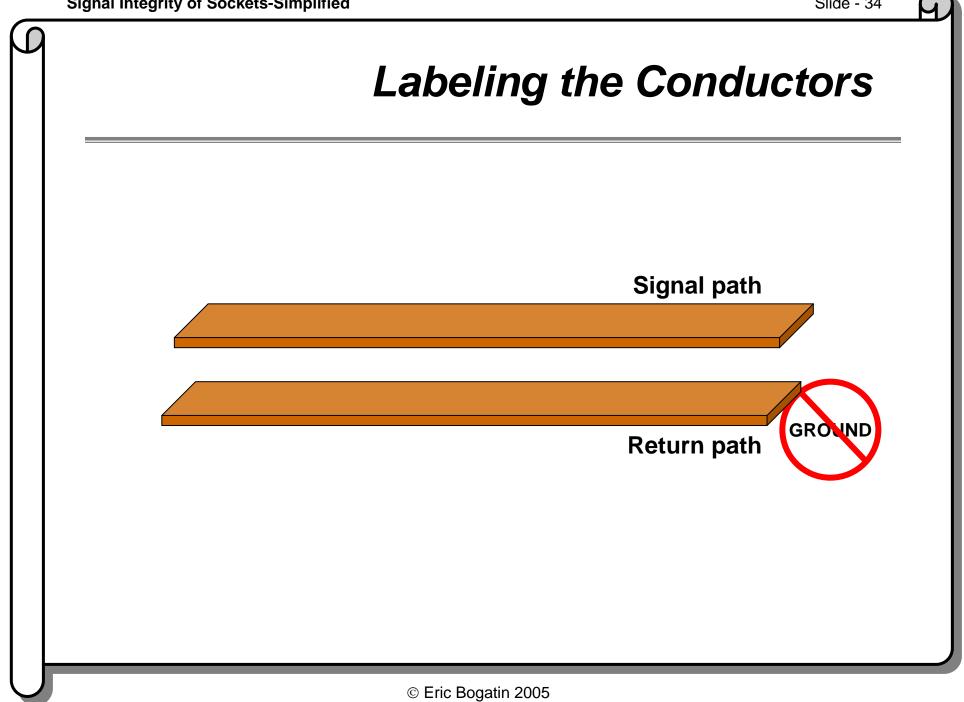

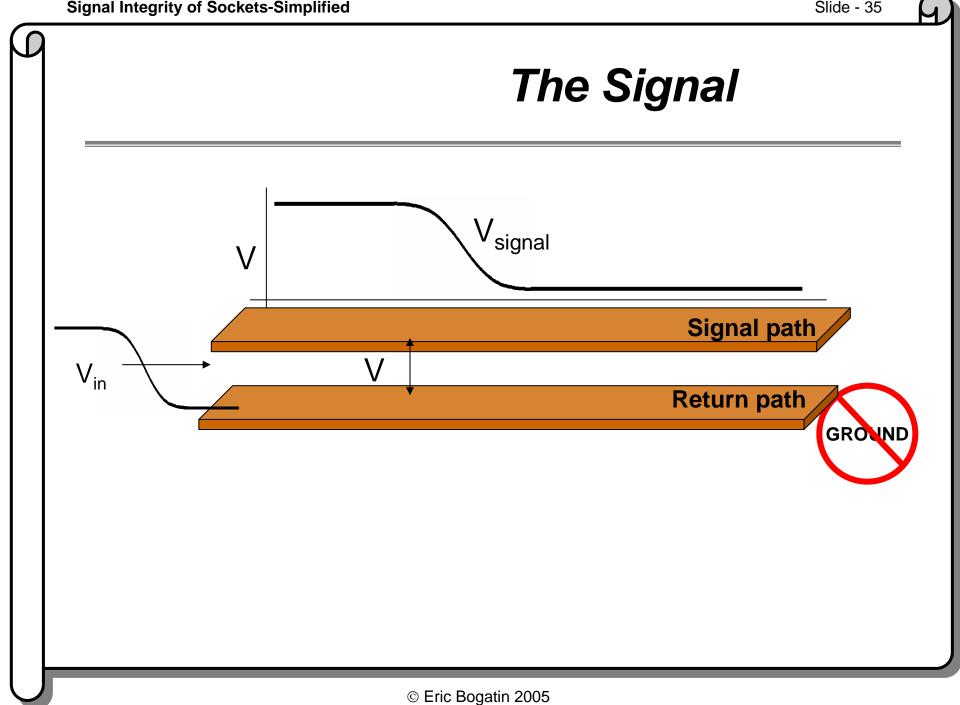

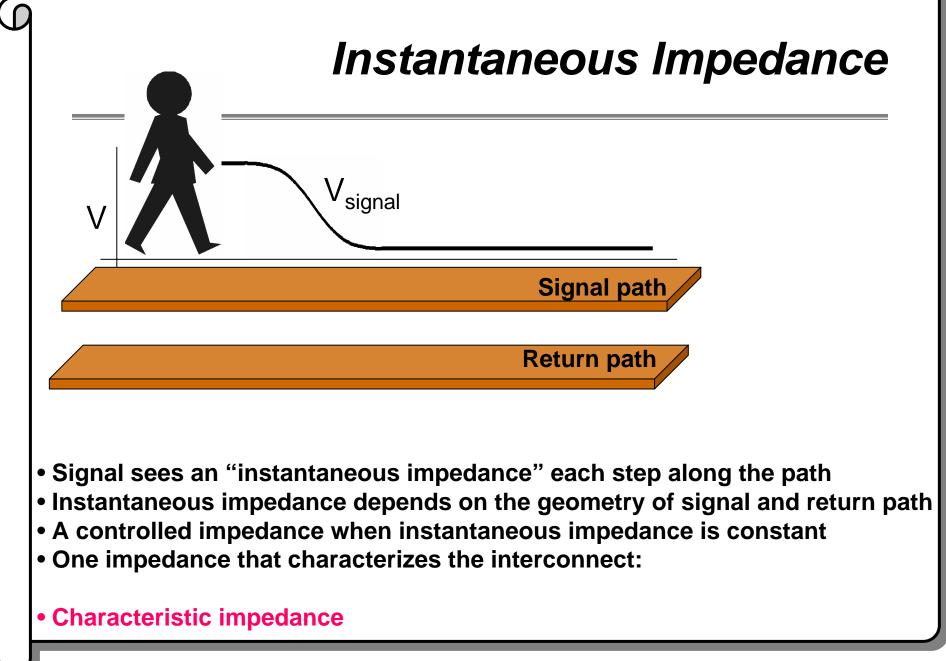

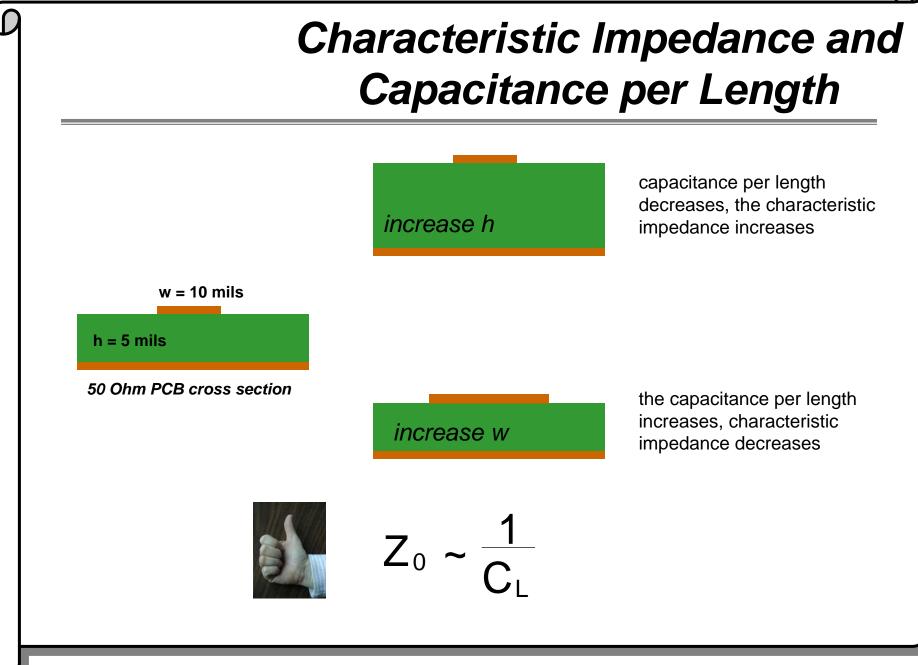

### Most Important Features of Characteristic Impedance

- Characteristic impedance is not about the signal path

- Characteristic impedance is not about the return path

- Characteristic impedance will depend both signal and return path, inseparably

- There is no such thing as the characteristic impedance of a single pin

- Change the return path configuration, you change the characteristic impedance

- (Obviously, the same goes for insertion loss!)

© Eric Bogatin 2005

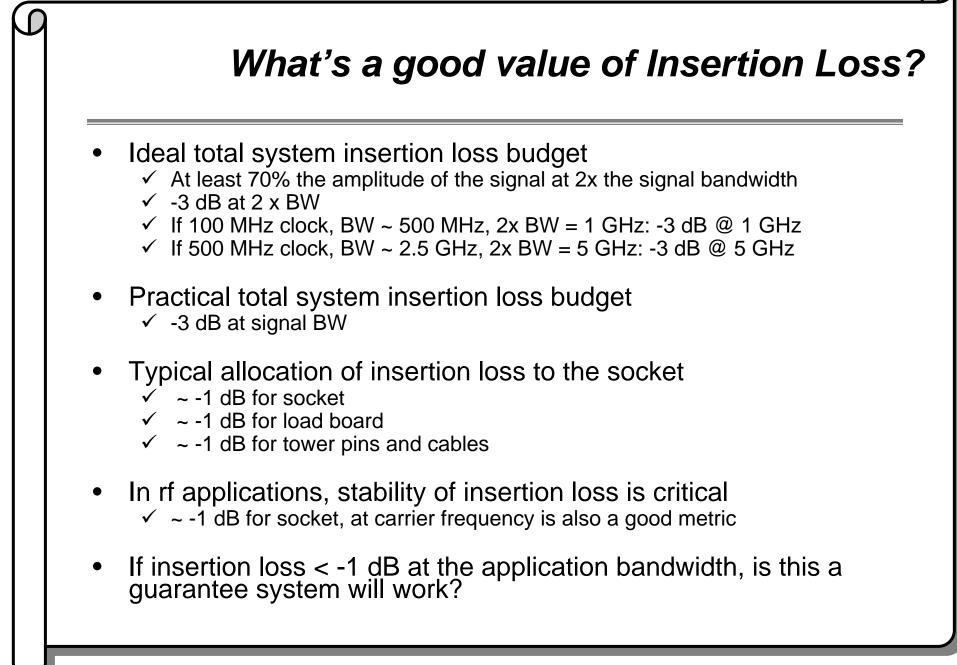

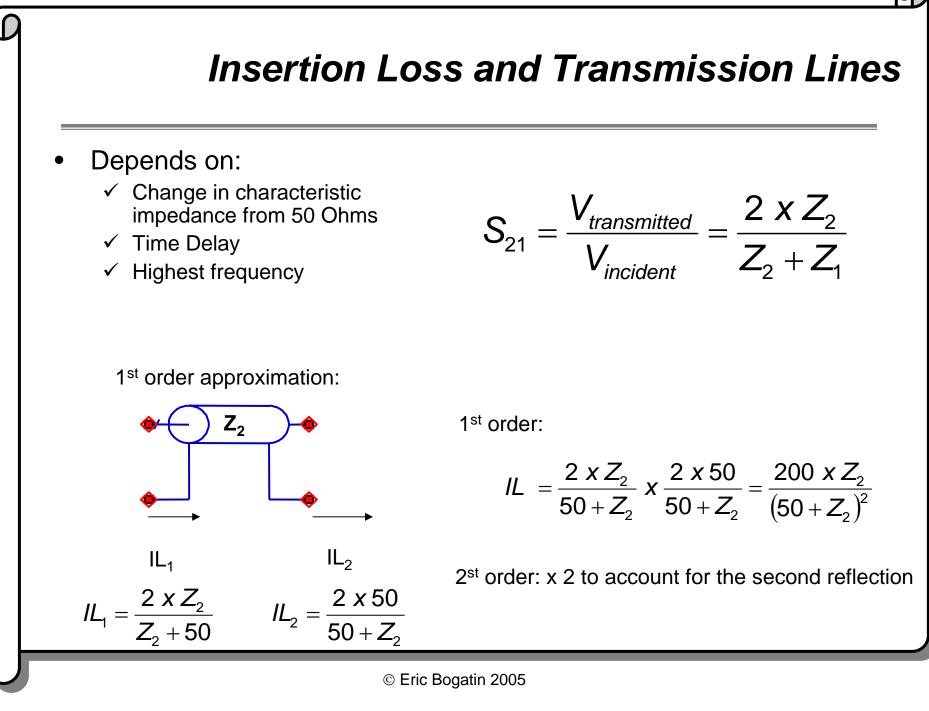

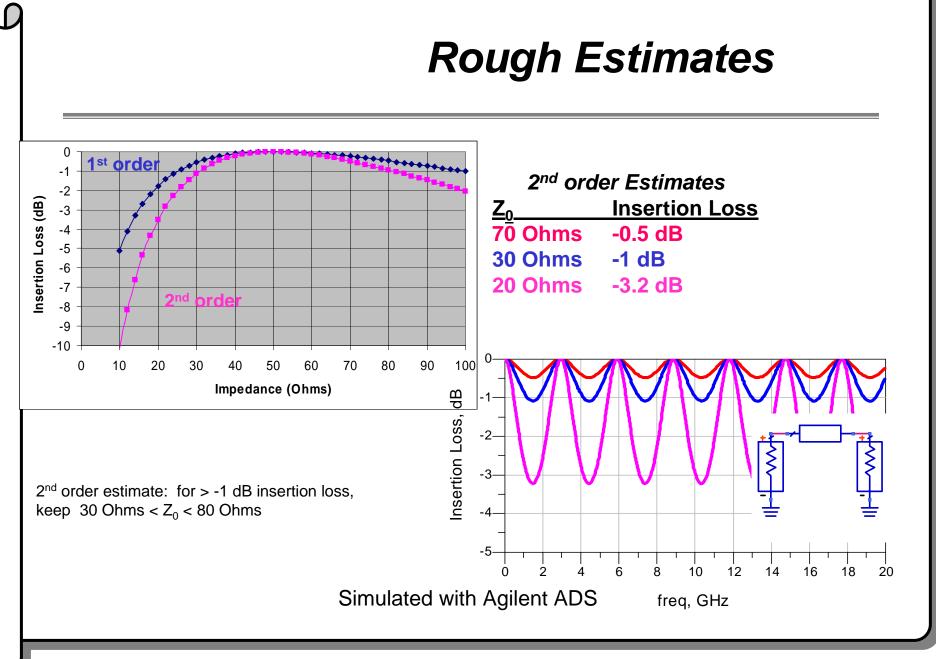

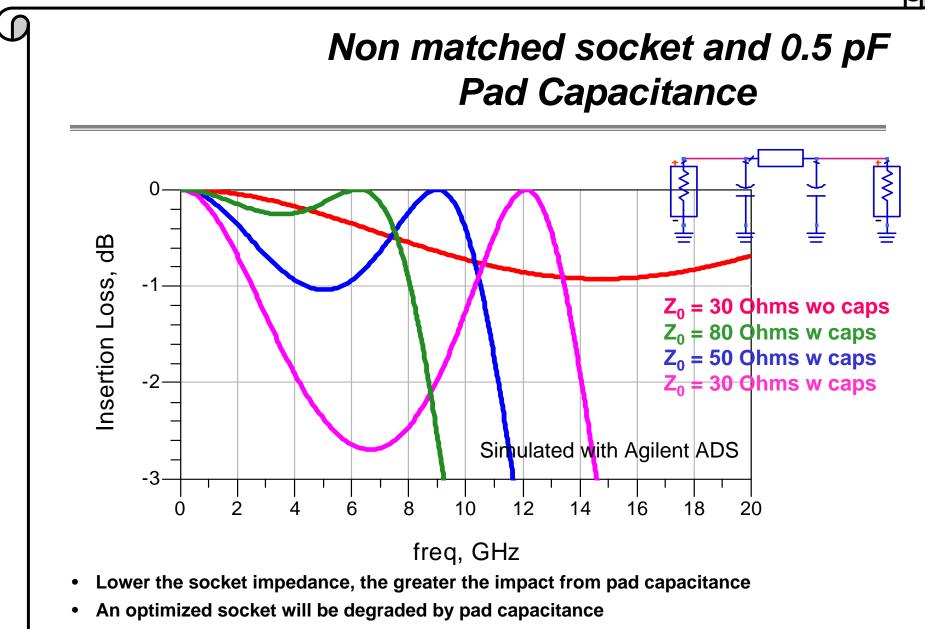

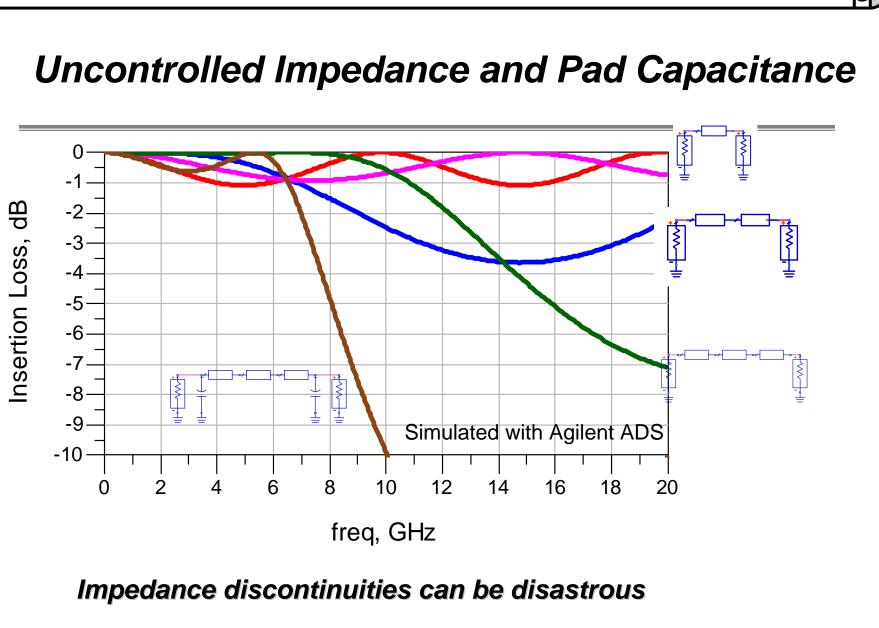

## Minimizing Insertion Loss Principle #1: Match Impedance to 50 Ohms

- 1. Uniform impedance interconnect

- 2. Match socket to 50 Ohms

- 3. Keep: 30 Ohms <  $Z_{\rm 0}$  < 80 Ohms and insertion loss will never be greater than -1 dB

freq, GHz

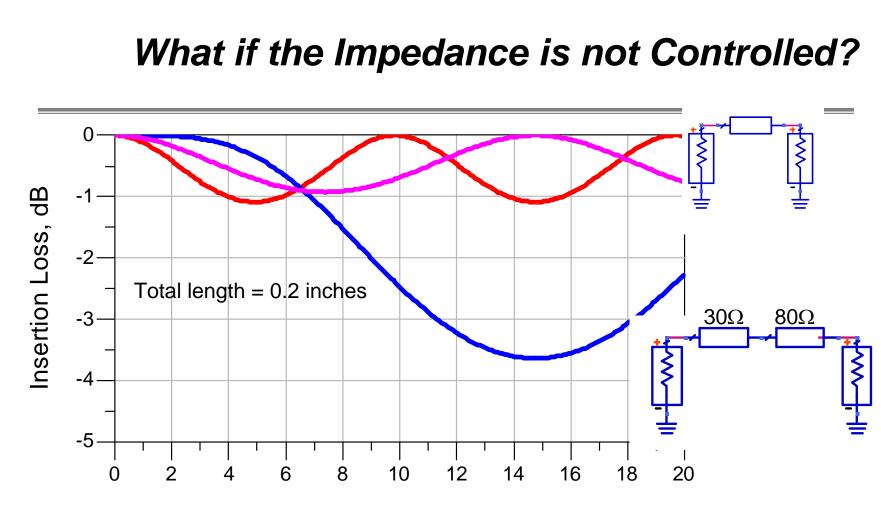

- Low frequency behavior is related to ~ average impedance- can be better than either one

- Highest insertion loss can be much worse than either discontinuity (> 3x)

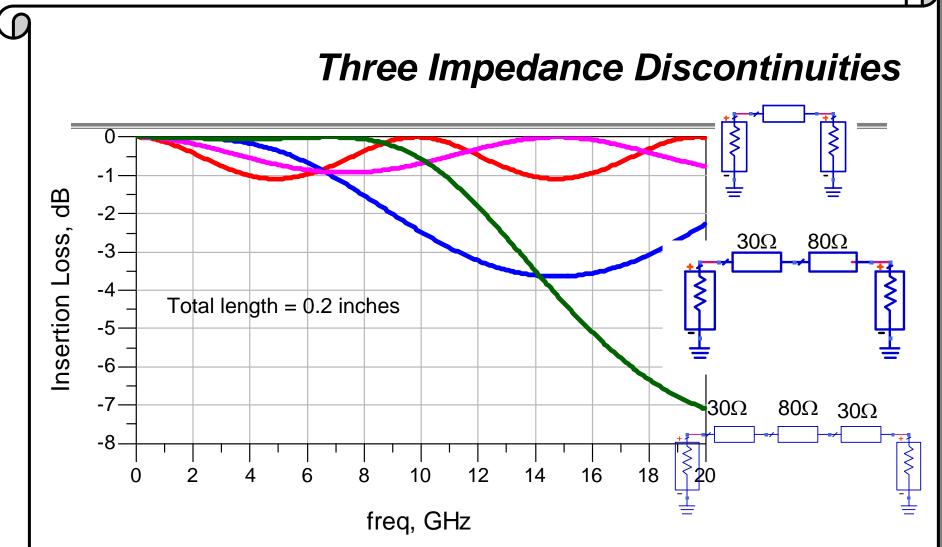

- Low frequency behavior is related to ~ average impedance- can be better than either one

- Highest insertion loss can be much worse than either discontinuity (> 7x)

μ

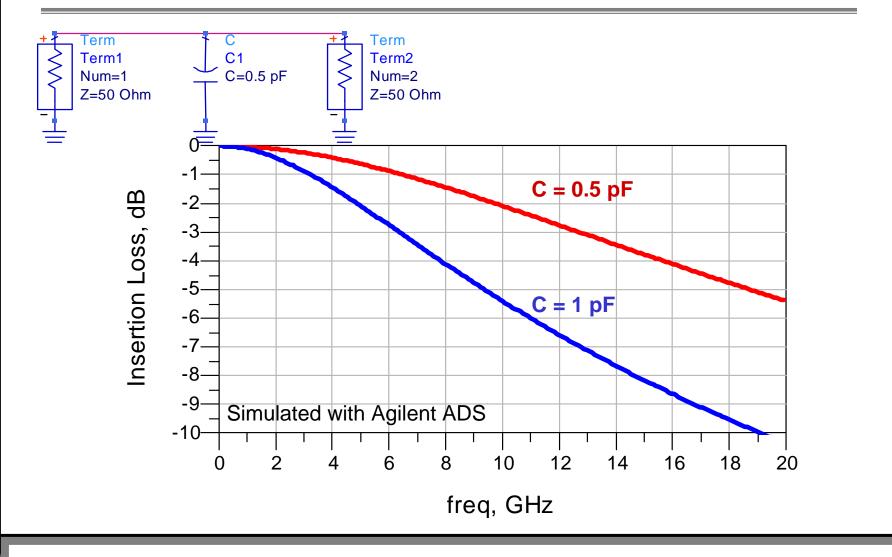

#### Insertion Loss from Pad Capacitance

$\ensuremath{\mathbb{C}}$  Eric Bogatin 2005

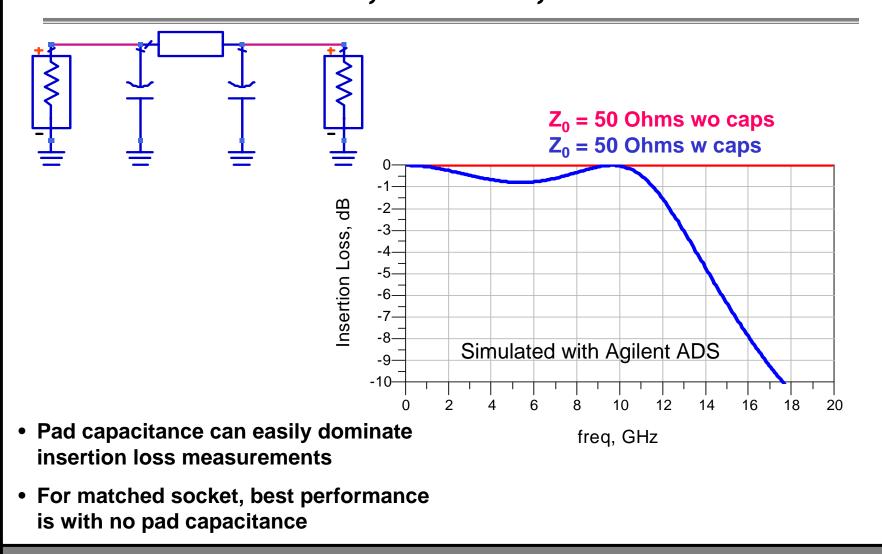

# Impact from 0.5 pF Pads on Either Side of 50 Ohm, lossless, Ideal Socket

### Minimizing Insertion Loss Principle #3: Minimize Pad Stack up Capacitance

- Pad stack up capacitance on test fixture/load board can and often does dominate insertion loss performance

- To first order, always try to minimize pad capacitance

- For best performance, optimize load board discontinuities to compensate: requires load board-socket-package co-design

- ✓ Use 3D full wave solver

- ✓ Use multiple test board launch designs to optimize pad stack up

- ✓ Change socket and compensation may be off

- ✓ When socket is well matched, performance is all about the load board

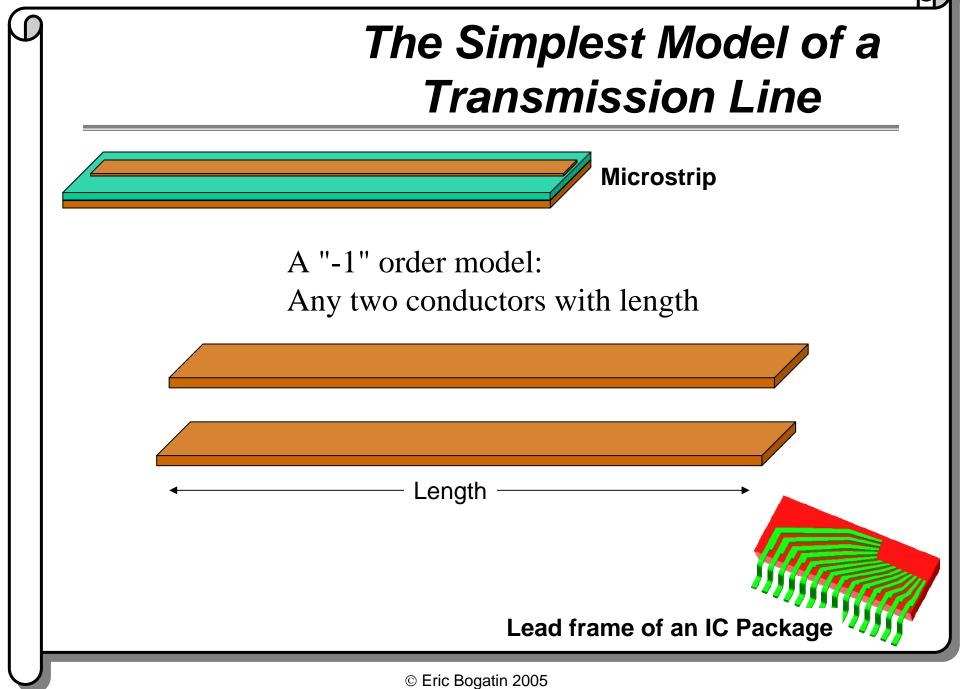

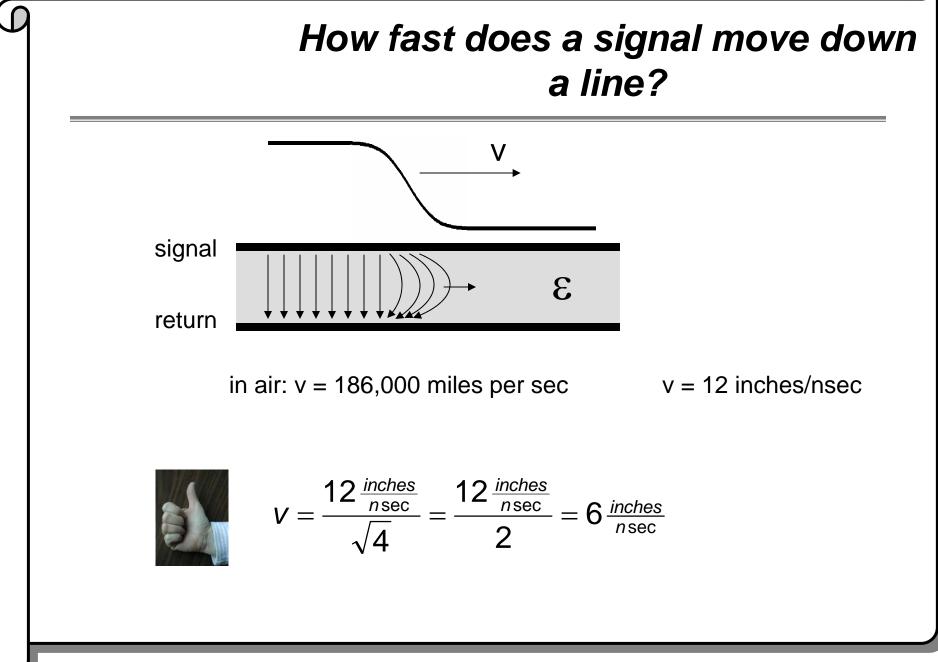

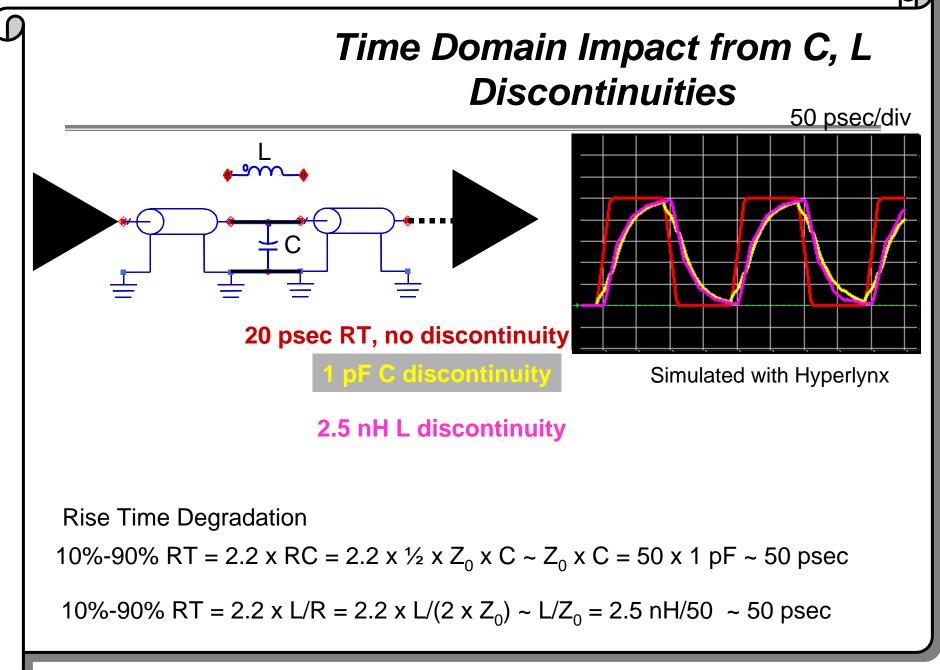

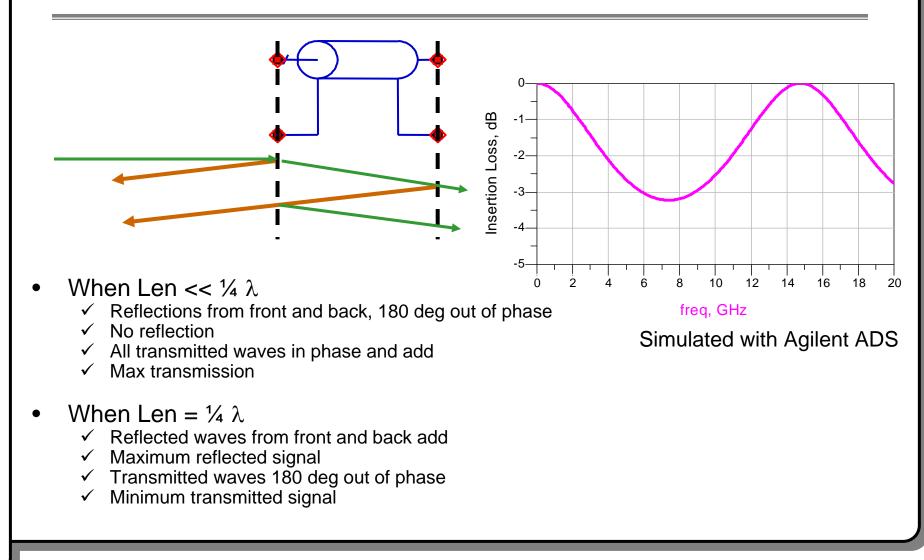

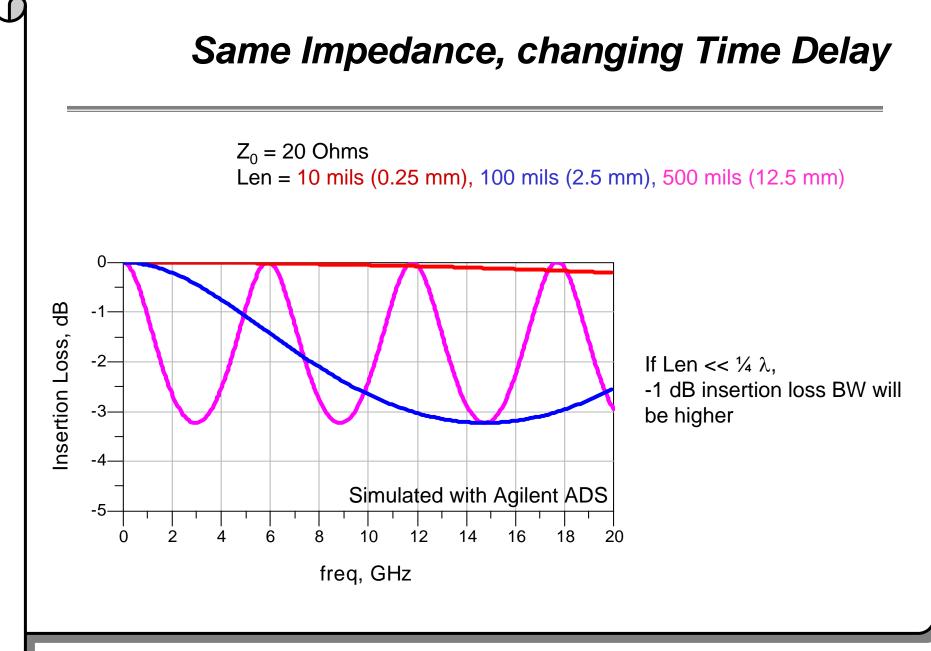

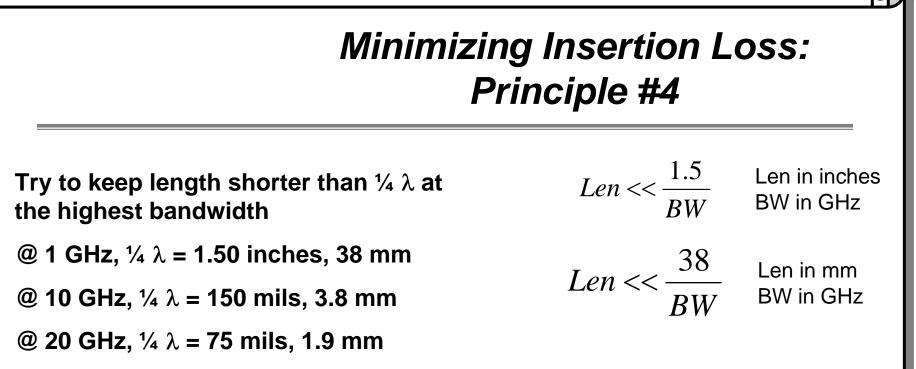

## Time Delay and Length

- Speed of signal ~ 6 inches/nsec = 150 mm/nsec in torlon, most polymers

- TD ~ Length / v = Len / 6 inches/nsec = Len x 160 psec/inch = Len x 6.7 psec/mm

- Len = 100 mils, TD = 16 psec

- Len = 3 mm, TD = 20 psec

TD ~ 160 psec/inch TD ~ 6.7 psec/mm

- If worst case insertion loss is less than -1 dB, TD may not be important

- If worst case insertion loss is greater than -1 dB, keep length << 1/4  $\lambda$

- Minimize insertion loss by keeping length << 1/4  $\lambda$

- Shorter is better, but long may be good enough

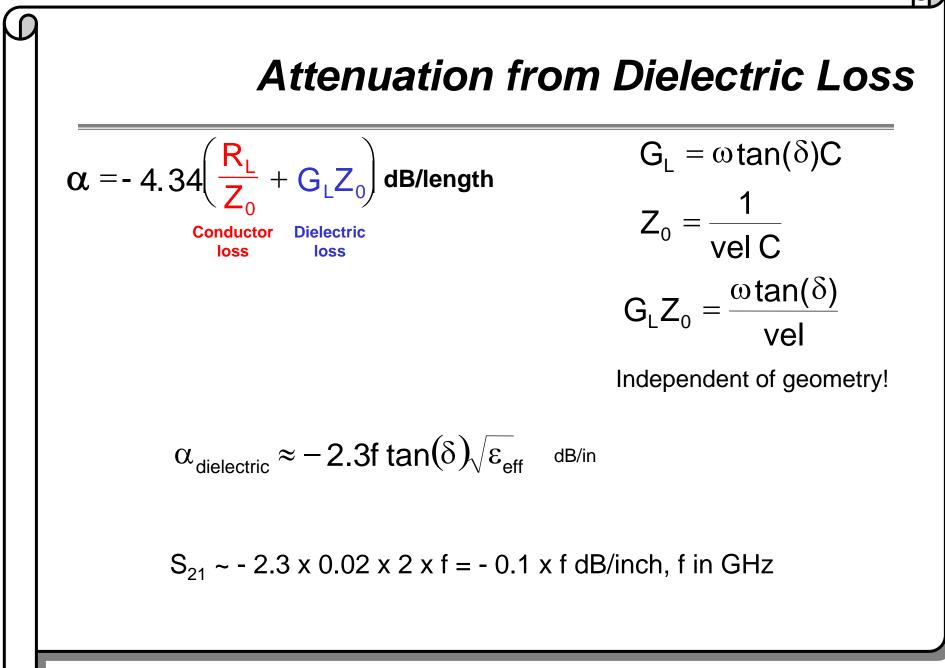

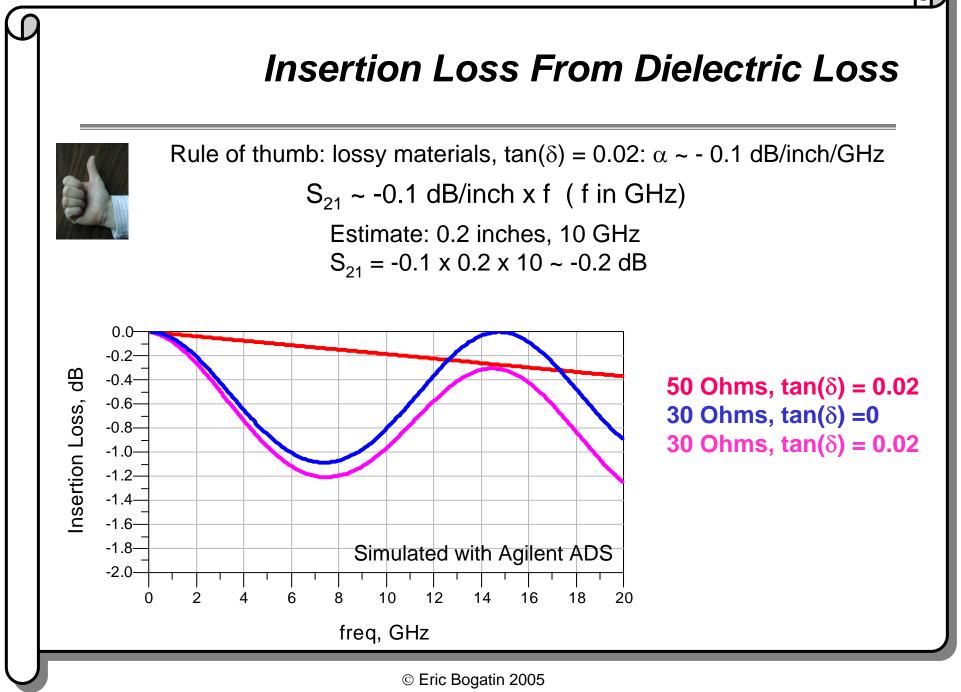

- If impedance is matched, dielectric loss is only a problem for very long interconnects (Len > 0.5 inches)

- If impedance is not matched, dielectric loss has small impact

- Shorter is always better, but long be good enough

<sup>©</sup> Eric Bogatin 2005

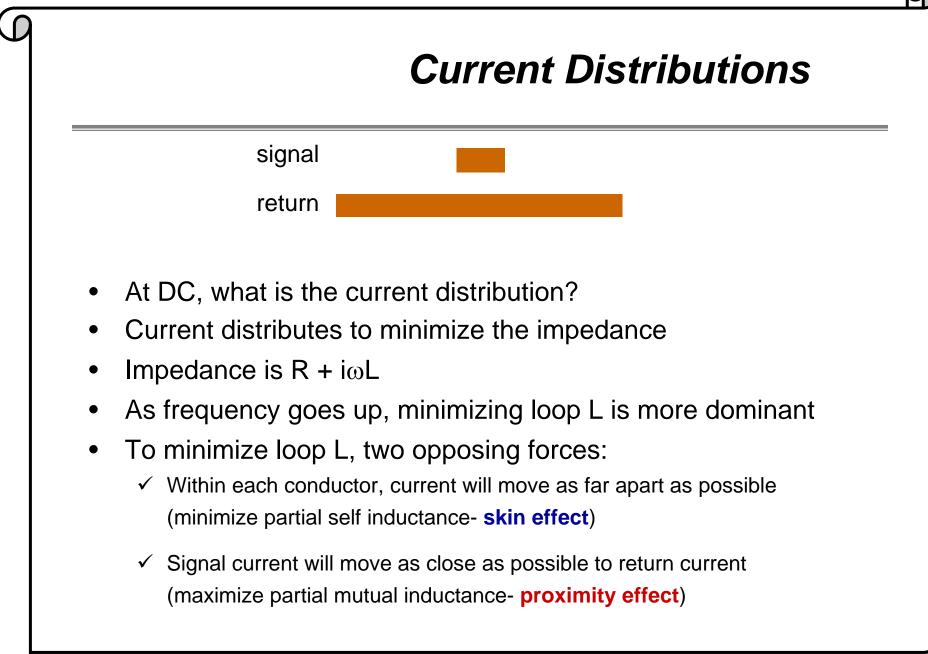

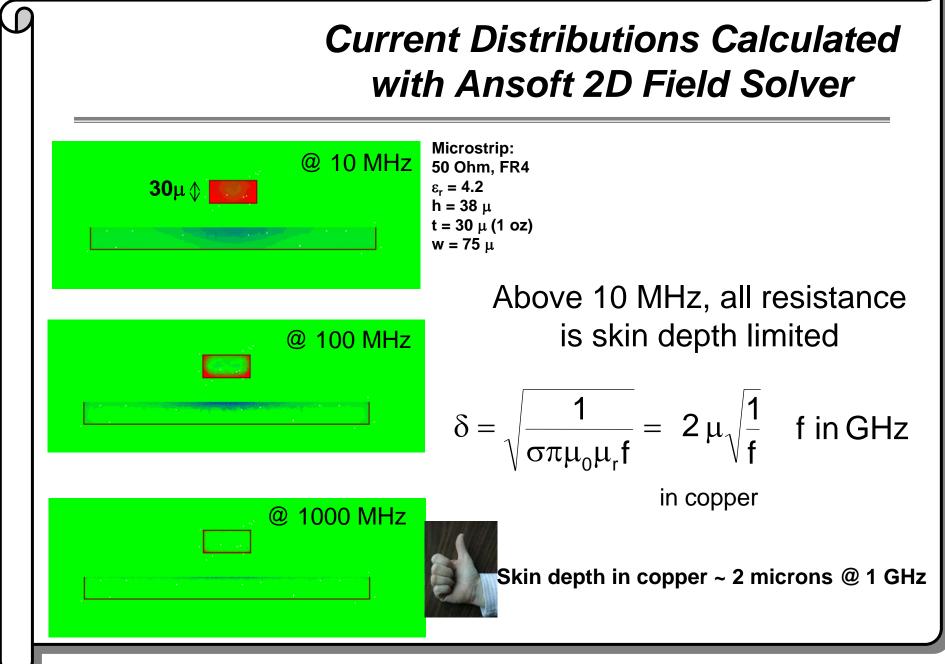

- Current distributions above 1 GHz are all skin depth limited

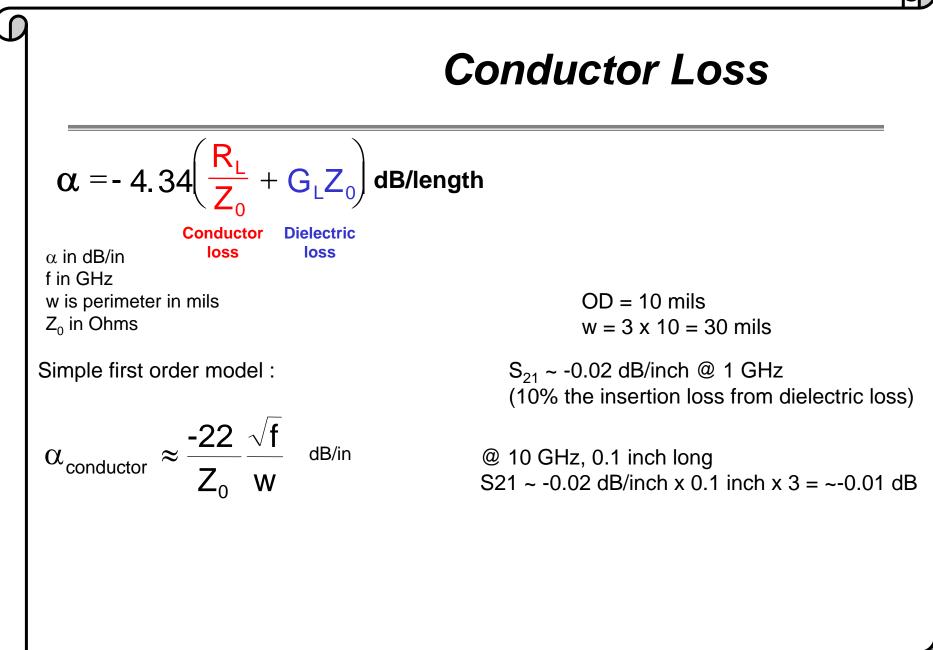

- Series resistance from skin depth has no impact on insertion loss for most structures with OD > 1 mils

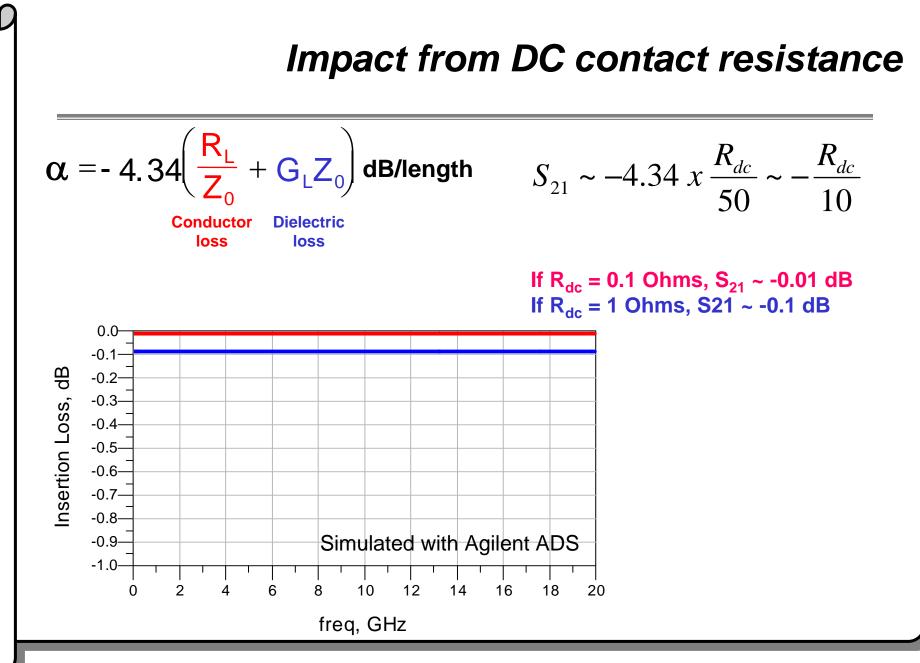

If contact resistance is so large that it affects insertion loss, you have a potential open problem, not an insertion loss problem

#### 7 Principles of Socket Design for Optimized Insertion Loss

- 1. match characteristic impedance of socket to 50 Ohms

- 2. Keep the impedance constant through socket

- 3. Optimize (minimize) pad stack up capacitance

- 4. Keep socket short

- 5. Dielectric loss of socket not critical

- 6. Conductor loss of socket not critical

- 7. Contact resistance of socket not critical

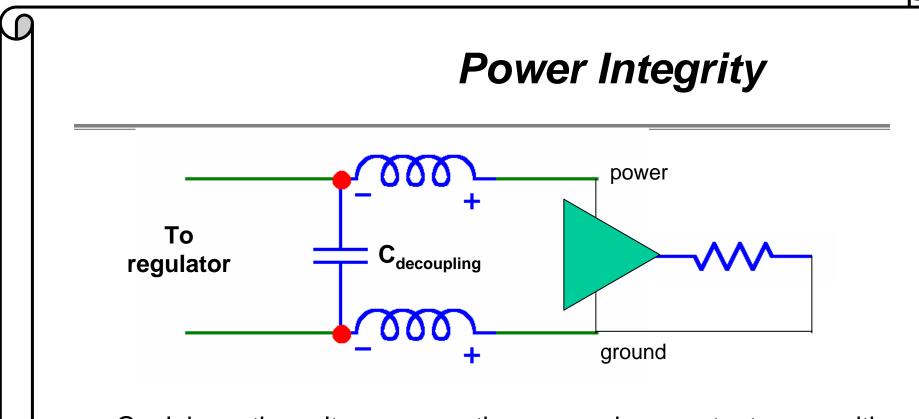

- Goal: keep the voltage across the power pins constant, even with current surges

- Strategy: minimize the impedance of the power distribution

- At high frequency,  $Z = R + i\omega L$

- L is the loop inductance of the power and ground return path

μ

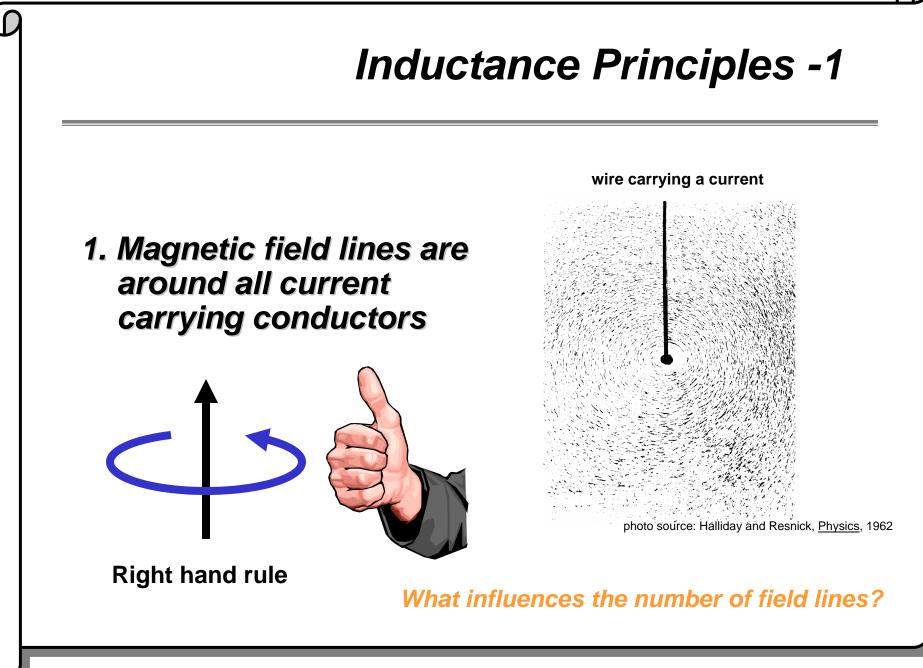

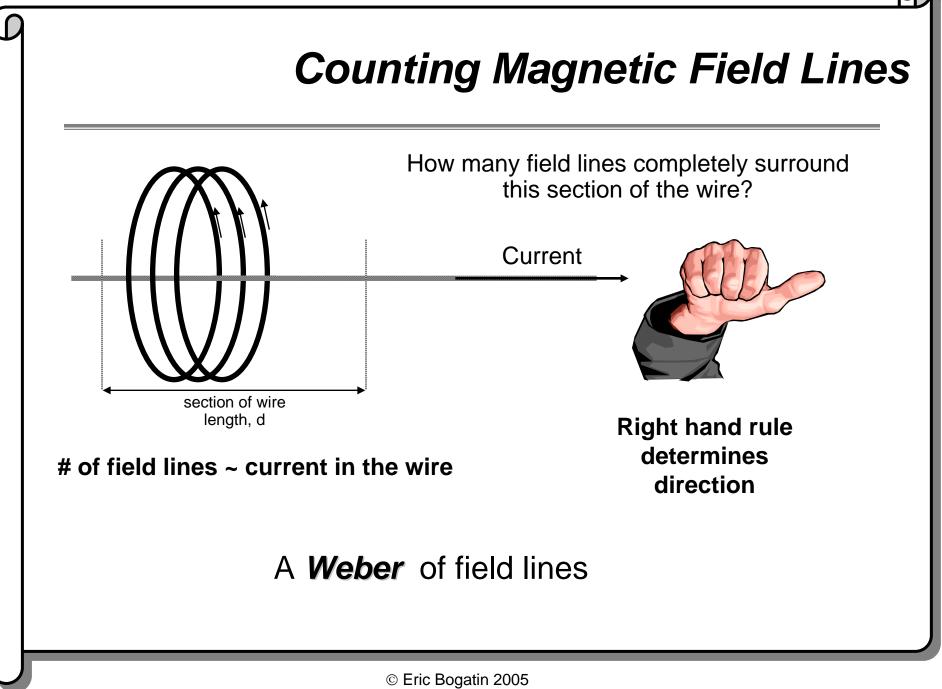

#### 2. Inductance is related to the number of field lines around the conductor, per amp of current through it

L = # of field lines around conductor, per amp of current

Units: Webers/amp = Henry nH more common

Many flavors of inductance: self - mutual loop - partial total, net or effective

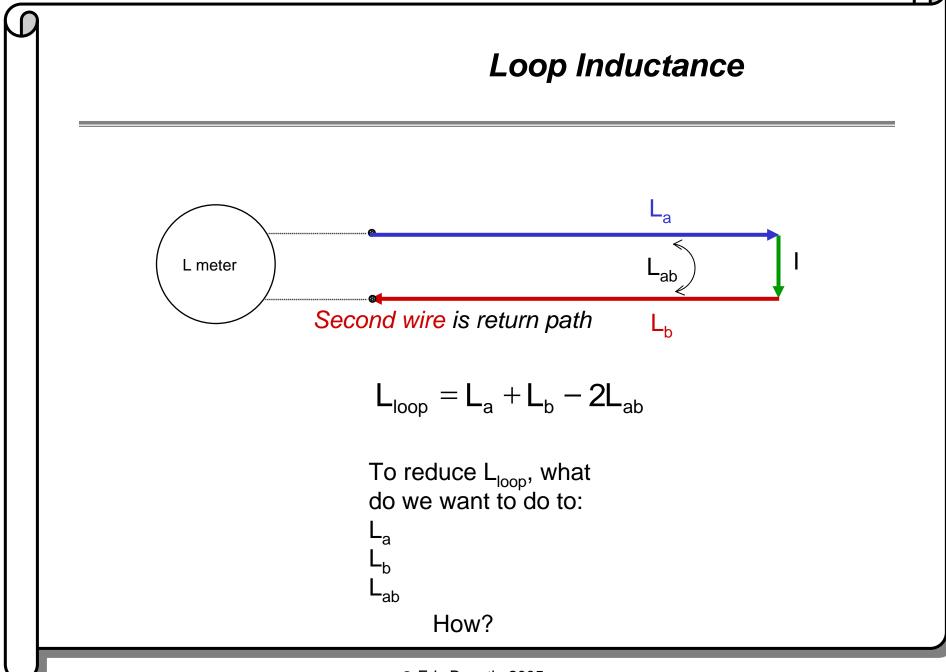

### Four principles for minimizing Loop Inductance

- 1. Short lengths

- 2. Wide conductors

- 3. Closely spaced return path

- 4. Multiple power-return conductors in parallel

#### Estimating Loop Inductance from Characteristic Impedance

- For any controlled impedance interconnect, by definition:

- ✓  $L_{loop} = TD \times Z_0$

- ✓ Example 1: 50 Ohms, TD ~ 20 psec,  $L_{loop} = 1 \text{ nH}$

- $L_{loop} \sim 170$  psec/inch x  $Z_0$  x Len = 6.8 psec/mm x  $Z_0$  x Len

#### • Examples:

$✓ Z_0 = 50 \text{ Ohms, Len} = 3 \text{ mm } L_{loop} = 6.8 \times 50 \times 3 = 1 \text{ nH}$   $✓ Z_0 = 50 \text{ Ohms, Len} = 1.5 \text{ mm } L_{loop} = 6.8 \times 50 \times 3 = 0.5 \text{ nH}$   $✓ Z_0 = 20 \text{ Ohms, Len} = 3 \text{ mm } L_{loop} = 6.8 \times 20 \times 3 = 0.5 \text{ nH}$   $✓ Z_0 = 50 \text{ Ohms, Len} = 0.1 \text{ mm } L_{loop} = 170 \times 50 \times 0.1 = 0.8 \text{ nH}$  $✓ Z_0 = 70 \text{ Ohms, Len} = 0.15 \text{ mm } L_{loop} = 170 70 \times 0.15 = 1.8 \text{ nH}$

- What does it mean to "work"?

- Signal integrity

- ✓ Insertion loss

- ✓ Bandwidth

- ✓ Characteristic impedance

- ✓ Time delay

- ✓ Dielectric loss

- ✓ Conductor loss

- Power integrity

- ✓ Loop inductance

- Other:

- ✓ Return loss

- ✓ Differential impedance

- ✓ Cross talk

- ✓ Ground bounce

www.BeTheSignal.com