# Burn-in & Test Socket Workshop

March 7 - 10, 2004 Hilton Phoenix East / Mesa Hotel Mesa, Arizona

ARCHIVE

# **COPYRIGHT NOTICE**

- The papers in this publication comprise the proceedings of the 2004 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

- There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

- The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

# **Technical Program**

#### Session 5 Tuesday 3/09/04 10:30AM

### MANAGING HIGH FREQUENCY REQUIREMENTS

#### **"Transmission Line Effects Of Nickel Plating In Contactor Applications**" Jon Diller – Synergetix Kevin DeFord – Synergetix

#### "Understanding The Effects Of Signal Path Bandwidth On **Semiconductor Test**"

Jason Mroczkowski – Everett Charles Technologies

#### "A Method For Contactor Characterization To 25 GHz"

**Tim Swettlen** – Intel Corporation **Orlando Bell** – GigaTest Labs Gary Otonari – GigaTest Labs

**Eric Bogatin** – Synergetix

Transmission Line Effects of Nickel Plating in Contactor Applications

2004 Burn-in and Test Socket Workshop March 7 - 10, 2004

Jon Diller and Kevin DeFord Synergetix

# Introduction

- Synergetix: Leadingedge since 1994

- Spring Contact Probe-based sockets

- RF expertise leads to Ni concerns

# **Concerns Regarding Nickel**

- High permeability

and resistivity

- Thin skin depth at high frequency

- Higher insertion loss

- Necessary as barrier layer and for hardness

## **Predicted Response**

- Best case (no Ni) @ 9 GHz

- $-R_{L}^{\sim}$  2.5 O / cm

- $-a_{L}$   $\sim$  0.25 dB / cm

- Total a ~ 0.06 dB

- Worst case, all current through thin flash (7  $\mu$  ") Au, a  $\,\widetilde{}\,$  0.25 dB

# **Test Subject**

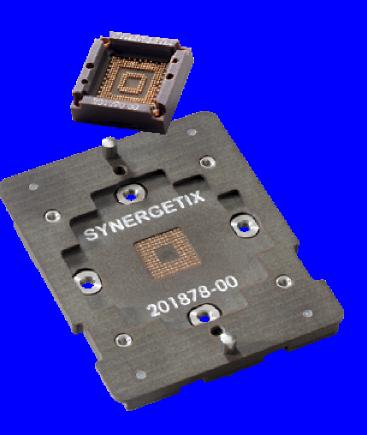

Probe: Ultra Micro **Pitch (101052)** - Moderate BW at 1 mm pitch - Good DC & life performance – In use at concerned customer

2,92 (.115) or 3,38 (.133) (.133) 0,25 (.010)

# **Test Subject**

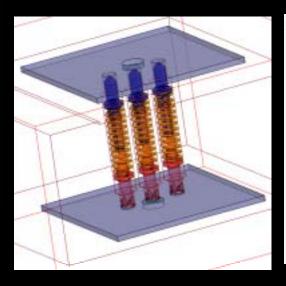

- Three-piece design

- Floats in test socket

- Plunger-barrel electrical path

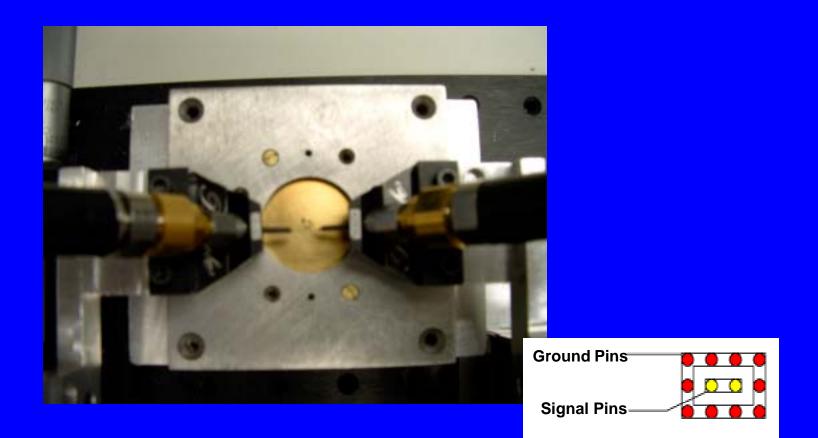

# **Test Concept**

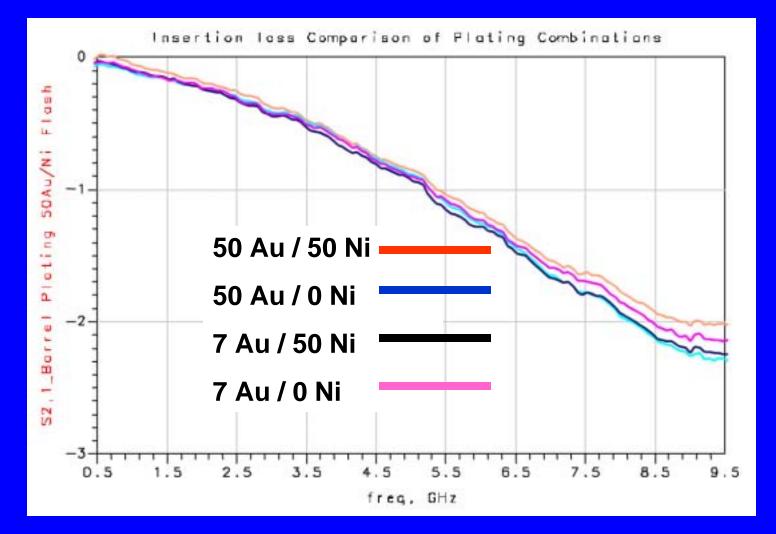

- Probes with various platings

- Measure S21 with HP8719 VNA

- Agilent ADS

- Measure

repeatability

- Compare platings

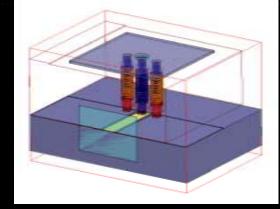

# **Test Setup**

# **Probe Configurations**

| Pin | Au Thickness   | Ni Thickness   |

|-----|----------------|----------------|

| 1   | 50 μ" (1.3 μm) | 50 μ" (1.3 μm) |

| 2   | 50 μ" (1.3 μm) | None           |

| 3   | 7 μ" (0.1 μm)  | 50 μ" (1.3 μm) |

| 4   | 7 μ" (0.1 μm)  | None           |

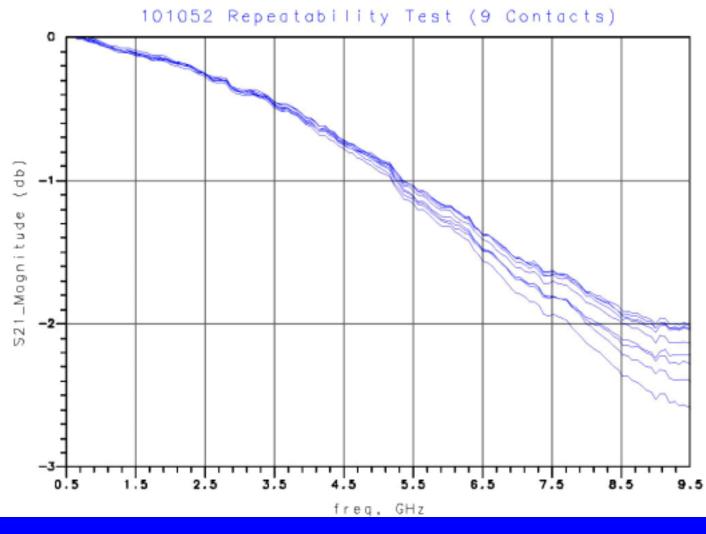

# Repeatability

19 Jan 2004

T/L Effects of Ni in Contactors

#### Results

# Conclusion

- Nickel content has no significant effect on TL behavior

- Gold thickness variations also not significant

- Testing very repeatable

# EVERETT CHARLES TECHNOLOGIES Testing the Limits

Crosstalk

Litter

Package

Supply Transients

Connector reflections

Return discontinuities

Timing violations

Stubs

Package

leading

Understanding the effects of signal path bandwidth on semiconductor test

Jason Mroczkowski ECT-Semiconductor Test Group - MN

# **Presentation Topics**

Bandwidth Definition

Bandwidth limitations

Digital signal transmission

Noise effects

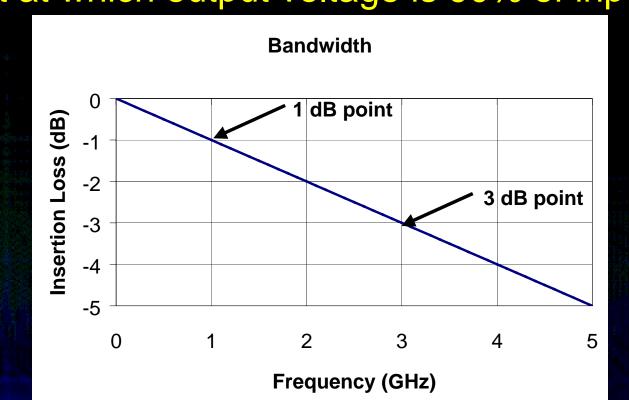

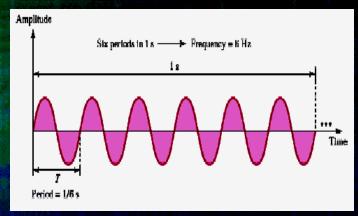

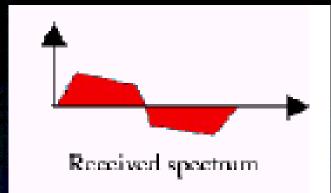

# Bandwidth

The range of frequencies that can pass through a conductor without significant degradation

The higher the bandwidth the greater the capacity in BPS.

Bandwidth

3 dB point

point at which power output is half the power input

point at which output voltage is 70% of input voltage

1 dB point

point at which output voltage is 90% of input voltage

4

# **Bandwidth limitations**

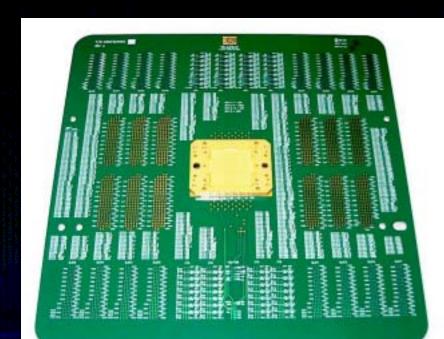

What causes bandwidth degradation ↗ inductance, capacitance, dielectric losses, skin effect, etc. **PCB** effects **7** Dielectric constant of PCB **Contactor effects** Dielectric constant of Contactor body quality of contact element (spring probe)

# System Bandwidth in Semiconductor test

#### At high frequencies, the board and contactor electrical performance interact.

- reflections at connectors

- -90 degree transition to contactor

# Insertion loss of contactor alone

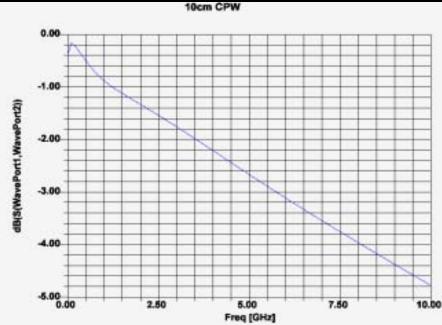

# Insertion loss of 25cm PCB alone

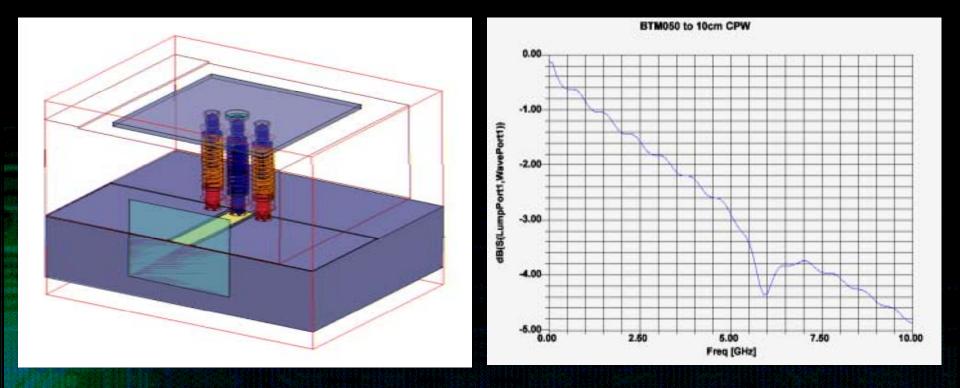

# Insertion loss of contactor and PCB together

# Bandwidth

compare board bandwidth to contactor bandwidth

**7** contactor - 2.54-6 mm

- more loss through board

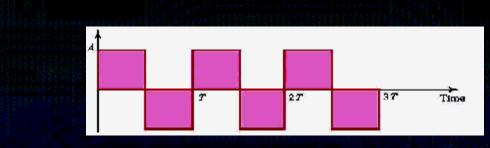

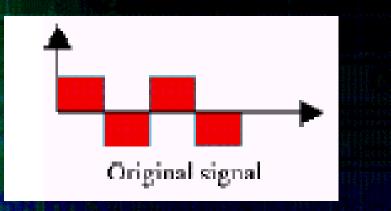

# **Digital Signals**

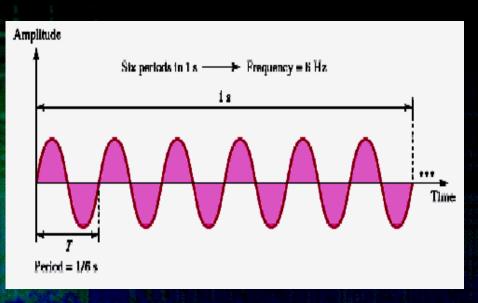

Analog signal

- A continuous signal that varies over time

- Sine wave represents an Analog signal

- Units of Hertz

- A sequence that has discrete values over time

- Square wave represents a digital signal

- 1 or 0 translated to voltage pulses over a conductor

# Units of Bits Per Second (BPS)

# Digital signals

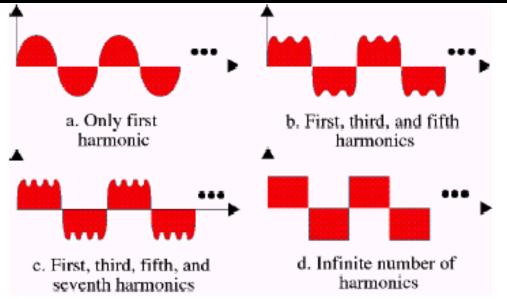

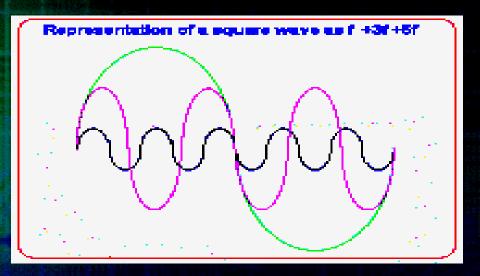

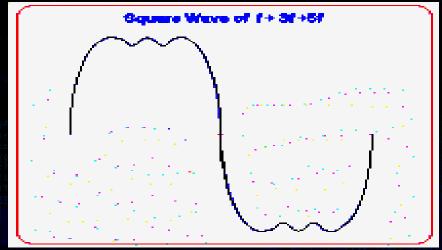

A Digital signal is made up of an infinite series of of sine waveforms (analog signals)

Y=cos(wt)-cos(3wt)/3+cos(5wt)/5-cos(7wt)/7 ... (etc.)

To perfectly represent a digital signal a transmission line must pass all frequencies of sine waveforms

# Digital signals

Minimum Harmonics to represent Digital signal

base frequency

1/2 bits per second rate

need fundamental plus third and fifth harmonic

minimum necessary to retain data when converted to digital signal

# **Analog and Digital Signals**

#### Example

- $\varkappa$  1Gbps  $\rightarrow$  500MHz base frequency

- Need at least 2.5GHz analog bandwidth to transmit 1Gbps binary digital signal

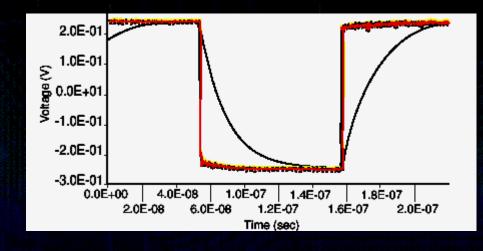

# Digital signal rise time

Relationship of Analog Bandwidth to Digital signal rise-time

¬ what bandwidth is required for certain rise time -BW = .35/Tr

Example

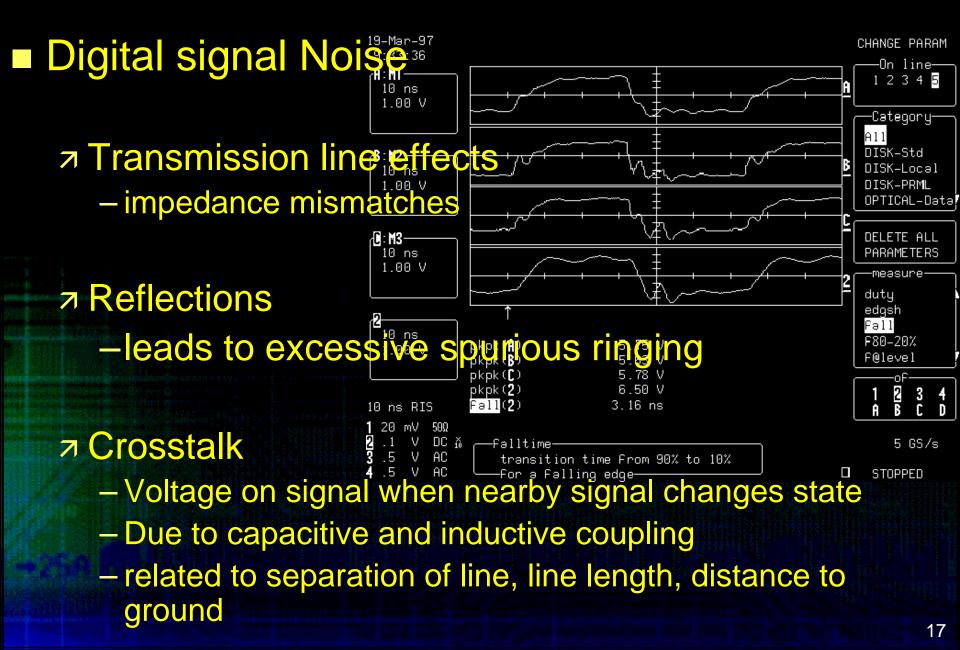

# **Digital signal Transmission**

- What degrades digital signal transmission ¬ Noise

- Sources of Noise

- Connectors, PCB trace layout, IC package geometry, power and ground planes

- Noise Effects

- Reflections, Crosstalk, ground shifts, inductive glitches

# **Digital signal Transmission**

Digital signal Transmission

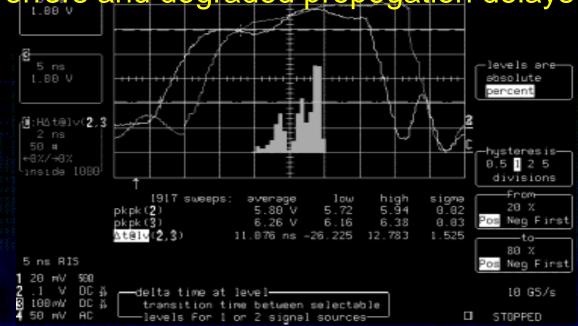

#### Digital signal Noise cont.

#### Ground bounces

- shifts in reference levels due to high frequency transients

- caused by large load currents

- results in logic errors and degraded propogation delays

# ¬ Thermal − White noise

SETUP ∆t@l∨

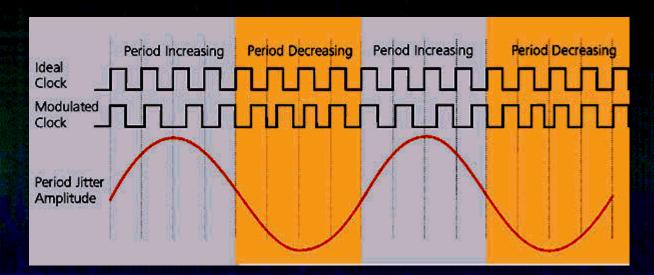

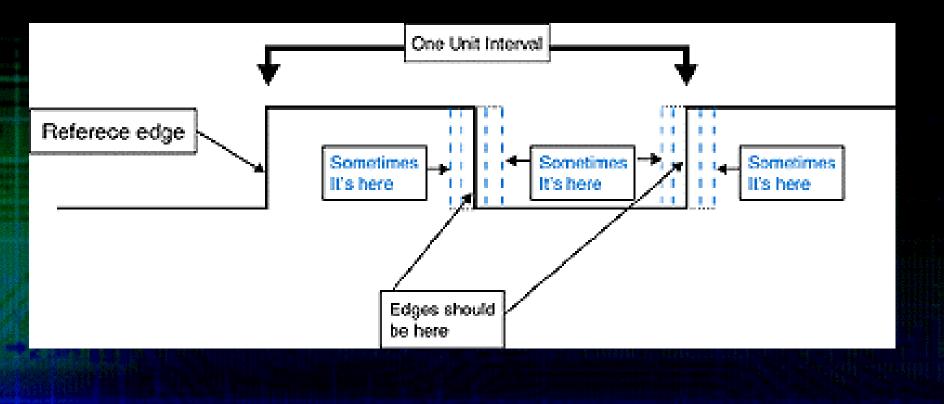

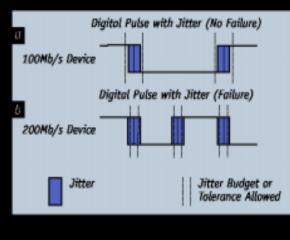

# **Jitter Definition**

The slight movement of a transmission signal in time or phase that can introduce errors and loss of synchronization.

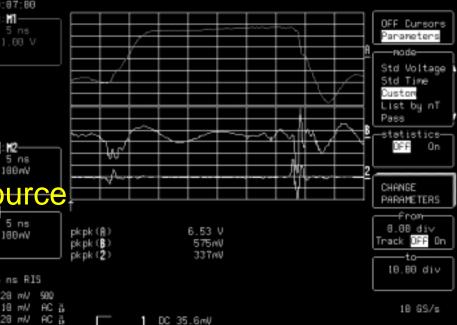

#### Digital signal jitter Sources of Jitter > Electromagnetic interference -switching power supplies - induces noise currents into signal conductor **¬** Crosstalk - magnetic and electric fields from adjacent signal -alter bias of signal 1.66 V **¬** Reflections - impedance mismatch - signal interferes with itself 188 eV - energy reflected back to source 5 ns 160 eV

MEASURE

STOPPED

# **Jitter**

Conditions that improve or degrade Jitter

Quality of the end termination in the tester

Quality of the device termination

Physical distance between the discontinuity and terminations

#### Occurrence of other discontinuities

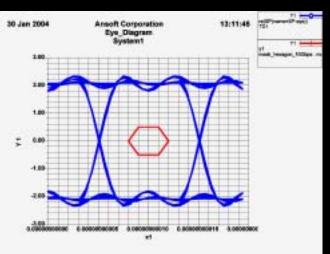

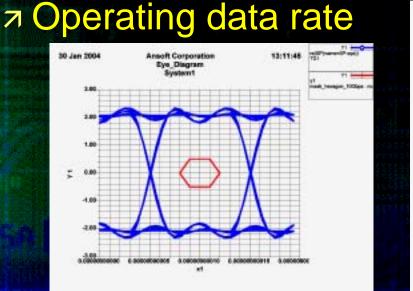

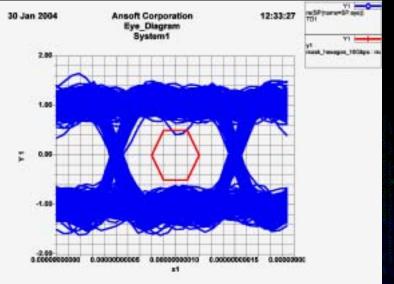

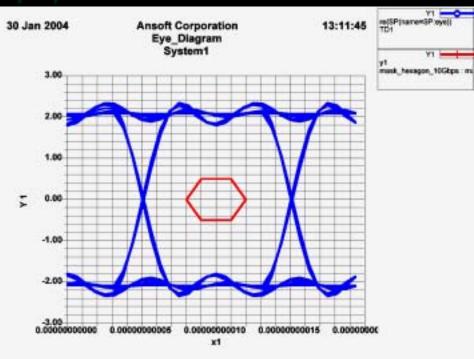

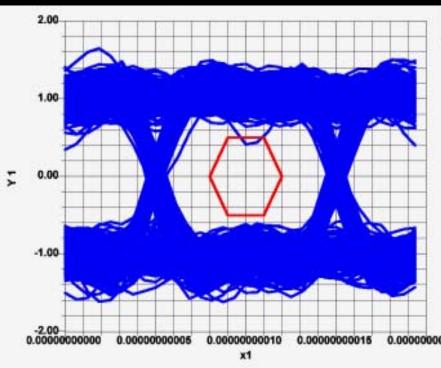

#### Eye Diagrams

# Ideal case no noise probes only

# Real case added noise added pcb

#### Future Design Challenge

- Optimize the interface between board and contactor

- A develop board trace characteristics that minimize the impedance mismatch

- ¬ 90 degree transition capacitive

- > compensate with trace termination geometry

#### Conclusions

- Board and contactor interact and therefore must be characterized together

- For successful digital signal transmission a conductor must pass at least the 5th fundamental

- Rise time limited by bandwidth

- Noise creates jitter which leads to digital signal errors

- Optimization of board to contactor transition to increase signal integrity

#### **References**

- "Jitter effects on Analog to Digital and Digital to Analog Converters", copyright 1999, 2000, Troisi Design Limited

"Measurement Challenges for On-Wafer RF-SOC Test", Wai Yuen Lau, Agilent Technologies, 1400 Fountaingrove Pkwy, Santa Rosa, CA 95403

- "DATA COMMUNICATIONS", v3.0 © Copyright Brian Brown, 1984-1997. All rights reserved.

- "Signals", Anan Phonphoem, Ph.D.anan@cpe.ku.ac.th, http://www.cpe.ku.ac.th/~anan, Computer Engineering Department, Kasetsart University, Bangkok, Thailand

# A Method for Contactor Characterization to 25 GHz

Tim Swettlen, Intel Corp. Orlando Bell, Gary Otonari, GigaTest Labs Eric Bogatin, Synergetix

March 21, 2004

- Driving forces on test socket requirements

- Existing Socket characterization techniques

- A higher bandwidth method

- An example

- Summary

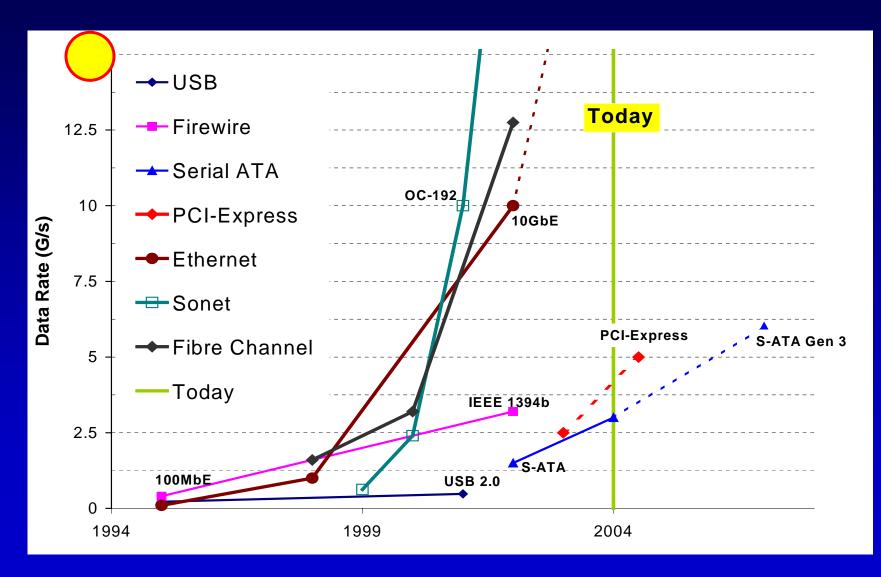

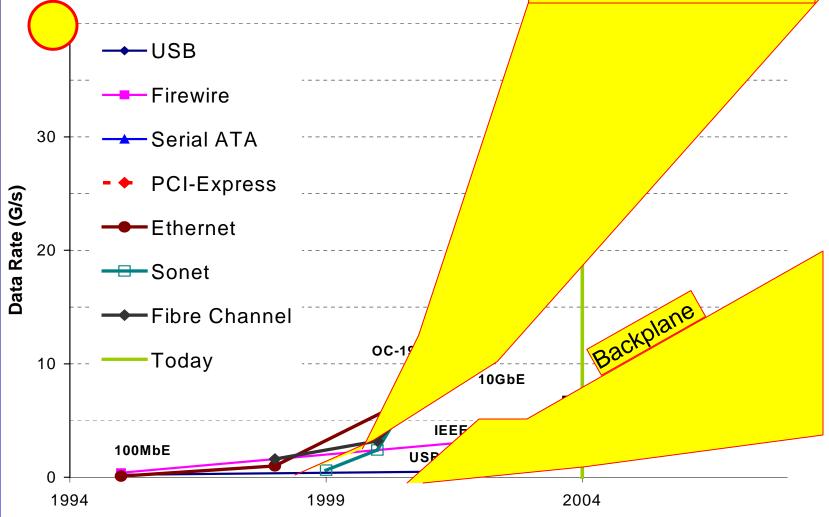

#### Increasing IO data rates

**BiTS 2004**

#### **IO** data rates... expanded

Communication window

# **The Challenge**

- To test these devices at speed, a socket is required

✓ Impact → socket must be well understood electrically

- Can have two independent requirements:

- ✓ Power/return pins:  $Z(f) \rightarrow 0$

- CRES stable and well below 50 mohms

- Loop inductance less than 3.0 nH

- ✓ Data rate pins,  $Z_0$  → 50 Ohms

- Insertion loss > 1 dB over the freq range

- Return loss < -15 dB over the freq range</p>

-- or --

Electrical lengths very short

• Data rate pins, up to at least the signal bandwidth

# Data Rate → Signal Bandwidth $F_{clock} = \frac{1}{2} \times Gbps$ $BW \sim (2 \rightarrow 5) \times F_{clock}$ $BW \sim (1 \rightarrow 2) \times Gbps$

#### Signal bandwidths will be > 20 GHz

# Covered in great detail in BITS 2003

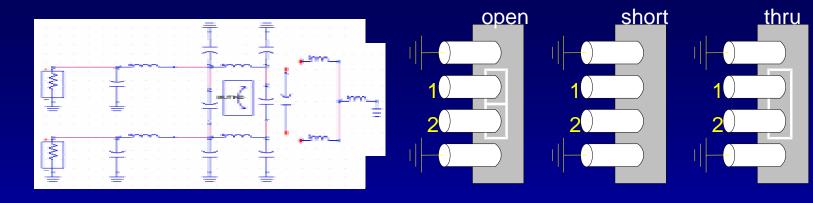

#### Traditional "High Bandwidth" Technique: open / short / loop thru

BW limitation is ability to model the surrogate chip

#### **2 Traditional Loop Thru methods**

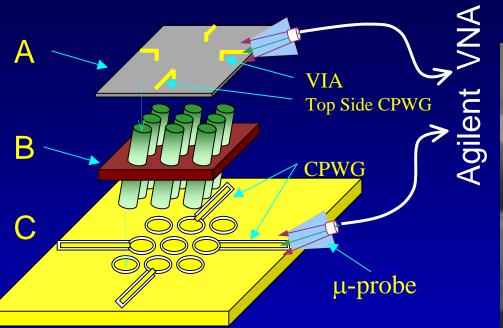

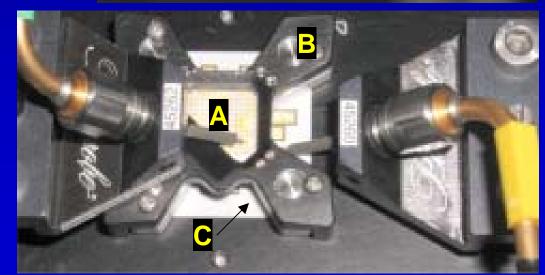

## Two port through

A → Surrogate Package B → Socket (DUT) C → Landing coupon

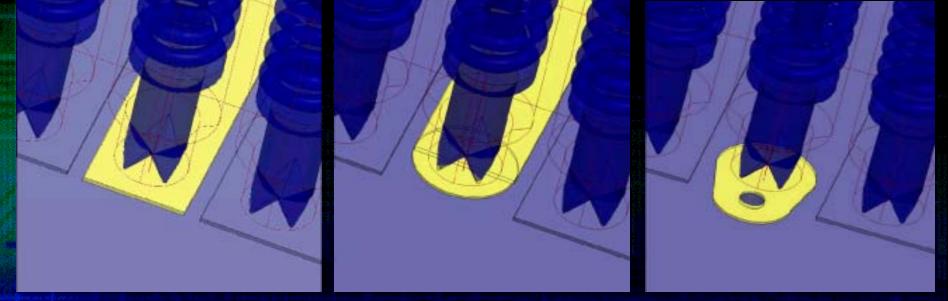

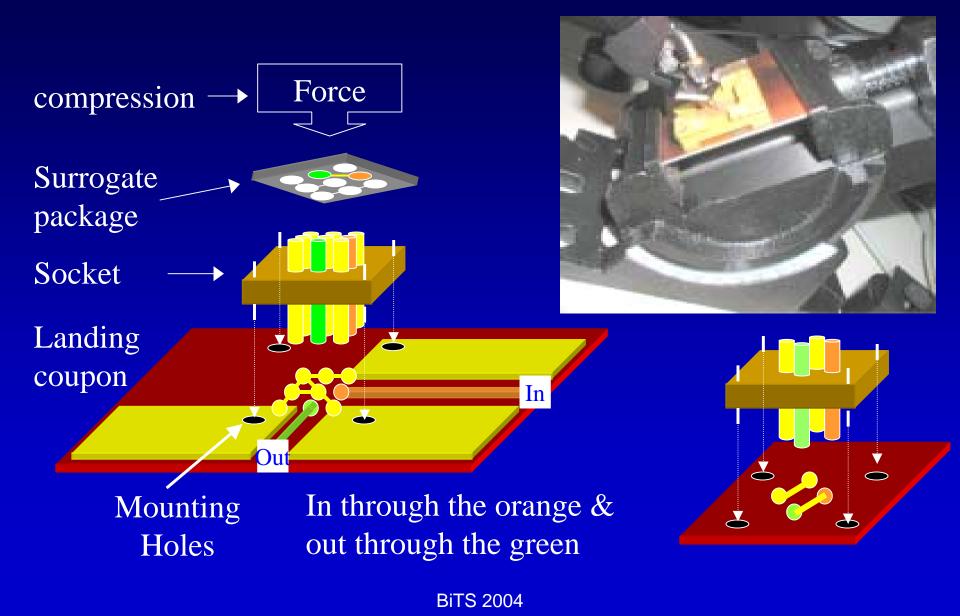

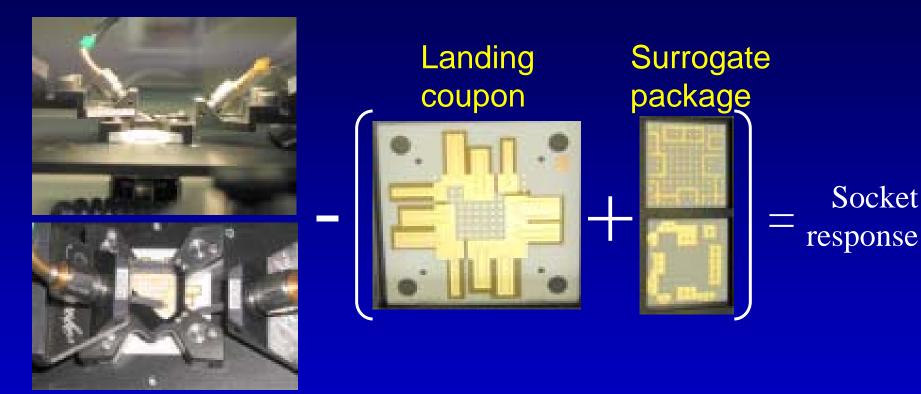

#### **One Higher Bandwidth Technique:** measure fixtures and de-embed

Measure complete system

Measure surrogate package and landing coupon, independently

Numerically extract just the socket

Socket

#### **Thru measurements**

| # | Description                                                                  | +'s                                                                                | -'S                                                                                                                                     |

|---|------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1 | TDR and measure risetime<br>(socket only)                                    | <ul> <li>Cheap and easy</li> </ul>                                                 | <ul> <li>BW is inferred from step risetime</li> <li>Pin-to-pin coupling not measured</li> <li>Fixture removal more difficult</li> </ul> |

| 2 | Two port thru<br>(socket only)                                               | •No extra hardware                                                                 | <ul><li>Difficult to probe 2 sides of socket<br/>simultaneously</li><li>Discontinuity at ref. plane</li></ul>                           |

| 3 | Two port loop bandwidth<br>(landing coupon or shorted package)               | •Relatively cheap<br>with mostly OTS<br>components                                 | <ul><li>Complex shorted package requires<br/>characterization and deembedding</li><li>Discontinuity at ref. plane</li></ul>             |

| 4 | <b>2-port open/short/thru</b> (loop)<br>(landing coupon + surrogate package) | •Measures pin-to-<br>pin and pin-to-<br>ground coupling                            | <ul> <li>Assumes thru = ½ loop</li> <li>Open/short/thru require<br/>characterization/deembedding</li> </ul>                             |

| 5 | <b>Two port through</b><br>(landing coupon + surrogate package)              | <ul> <li>Most expensive</li> <li>Most controlled /<br/>highest accuracy</li> </ul> | •Coupon and surrogate only<br>approximately emulate actual<br>package and board                                                         |

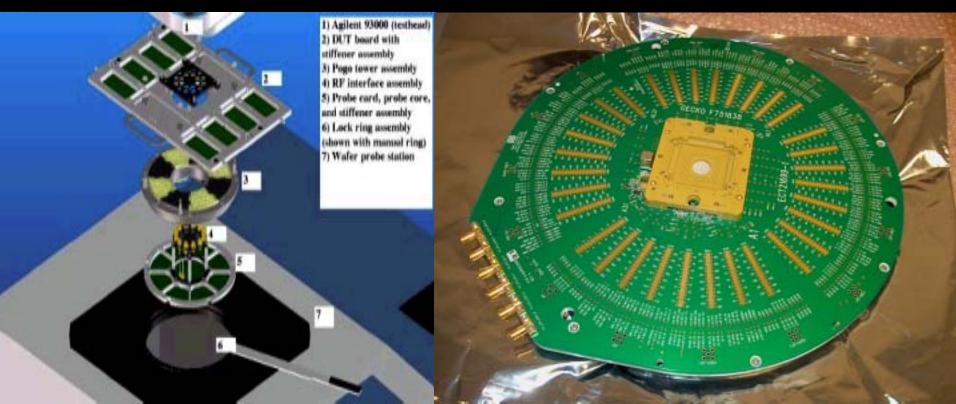

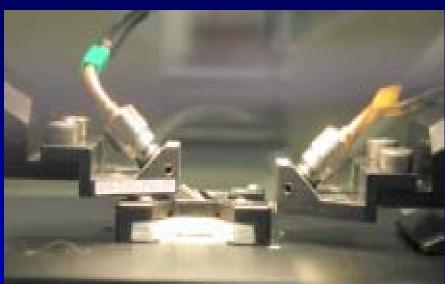

#### **Measurement System**

#### • Equipment list:

- ✓ GigaTest Labs Probe Station

- ✓ 35 GHz coaxial cables (3.5mm SMA connectors)

- ✓ Agilent Technologies 8510C VNA

- ✓ GGB probes, qty=2 (part number 40A-250-GSG-DP)

- Cascade Microtech LRM calibration substrate

- Cascade Microtech Wincal LRM calibration program

- ✓ Agilent Advanced Design System software (ADS 2002C)

- Measurements and analysis

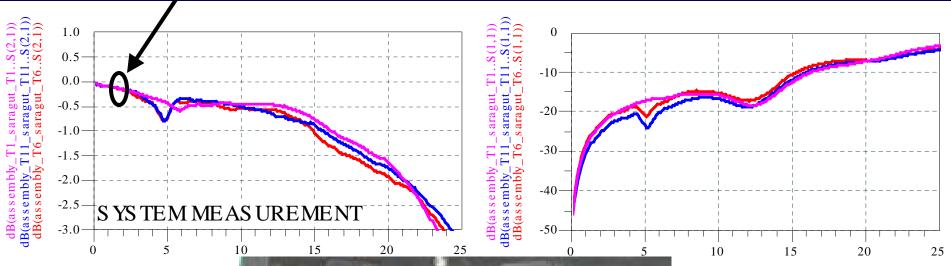

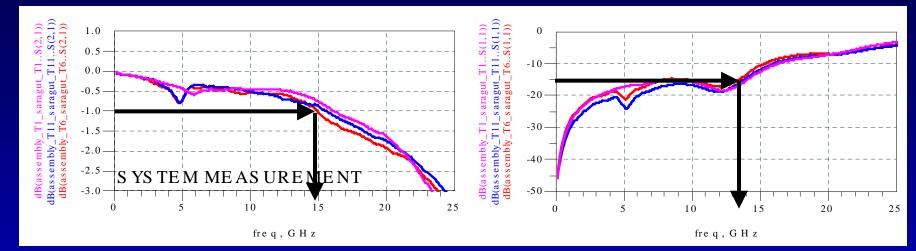

## System (Measured) Performance

#### 3 different single ended paths

freq,GHz

Slide - 14

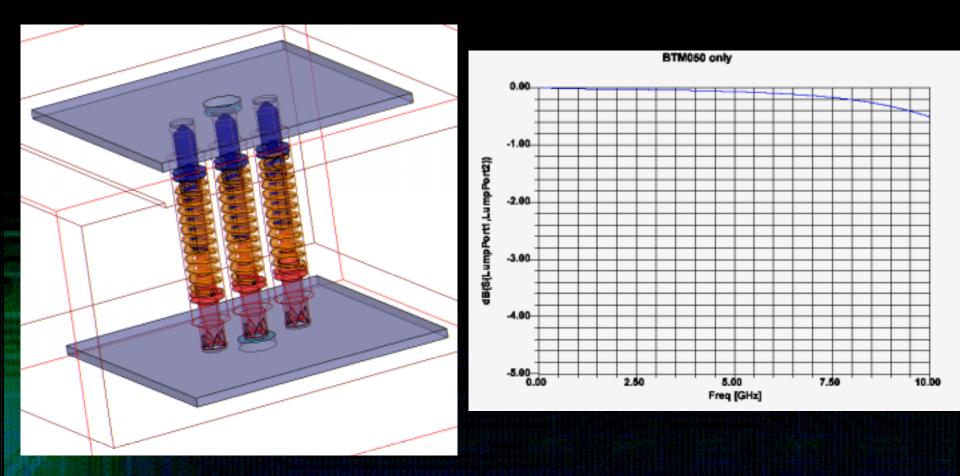

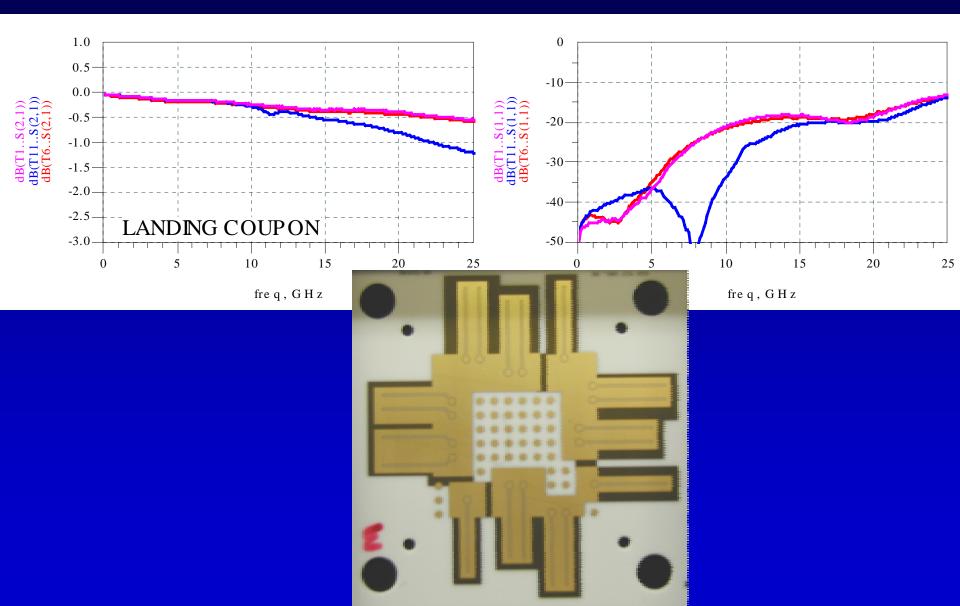

## Fixture, Landing Coupon

Slide - 15

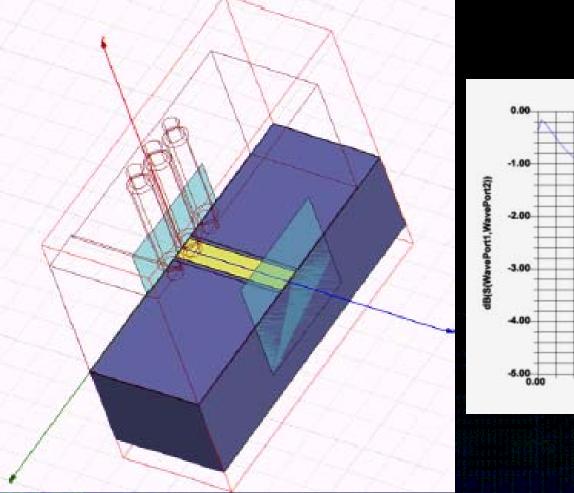

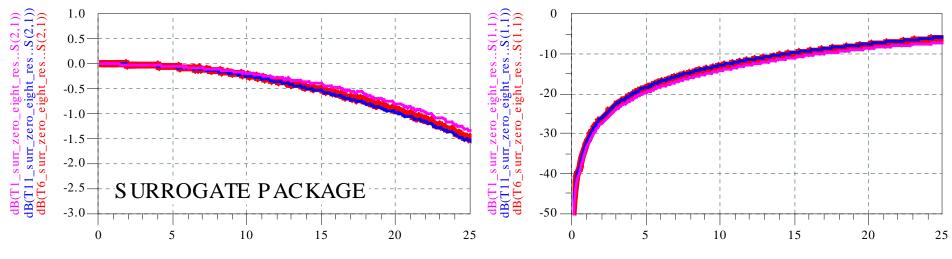

#### **Fixture, Surrogate Chip**

freq,GHz

freq,GHz

bottom

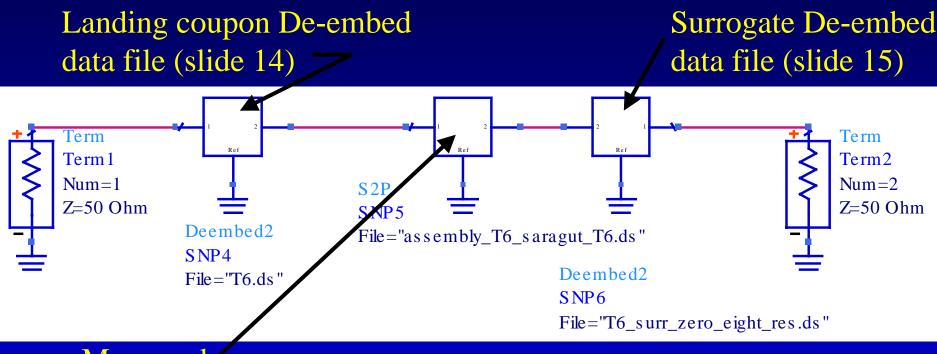

#### De-embed to Extract Just the Socket, in Agilent's ADS

Measured Fixture/Socket/Surrogate (slide 13)

Simulated S parameters of de-emedded socket only

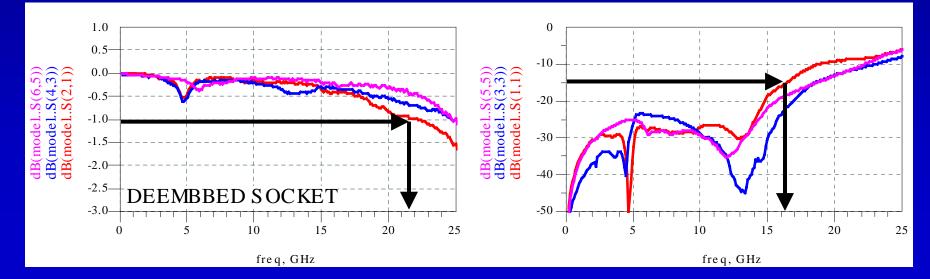

#### Through Path, De-emedded Socket Only

# **Strengths**

- Landing coupon and surrogate package are very clean well out to 25 GHz

- Allows for a fair "apples-to-apples" comparison of multiple sockets

- Removes any layout advantage one supplier may have over another

- Discontinuities at launch can be adjusted out if necessary

- Common for ref plane to be off from probe tip

#### Weaknesses

- Expensive; other options use either mechanical package samples or other 'cheap' fixtures

- Ceramics are not identical to final tooling environment

- Can't optimize the via/pad/pin as a system, only look at the pin independently.

- HTCC vias are poor. Surrogate package performance was weakest part

- More than two ports, <u>very</u> challenging to probe.

✓ Launches too close to each other to fan out

#### Next steps

• Second spin on the hardware

- Increased socket size, match mechanical socket samples

- ✓ Higher number of coupled lines

- More extensive usage of LRM and TRL calibration structures

- ✓LTCC verse HTCC tradeoffs

## Conclusions

- Application bandwidths will only increase

- New characterization techniques need to evolve with new socket technologies

- The fixtures used to facilitate the measurements are as critical as the socket itself.

- Measuring each component and de-embedding techniques have a useful bandwidth above 25 GHz