# Burn-in & Test Socket Workshop WELCOME

March 2 - 5, 2003 Hilton Phoenix East / Mesa Hotel Mesa, Arizona

Sponsored By The IEEE Computer Society Test Technology Technical Council

tttc<sub>TM</sub>

# BITS

#### **COPYRIGHT NOTICE**

• The papers in this publication comprise the proceedings of the 2003 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, or the Institute of Electrical and Electronic Engineers, Inc.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, proper acknowledgement should be made to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

#### **Technical Program**

#### Session 1 Monday 3/03/03 8:30AM

#### **Test And Burn-in Operations**

"Full Wafer Contact Burn-In And Test - The Ultimate In Parallelism" Steve Steps - AEHR Test Systems

"Strategic Use Of Burn In"

Tamas Kerekes - NplusT Semiconductor Application Center S.r.l.

"A Flexible Electrical Interface Design For The Fixture Between Tester And DUT To Achieve Reduced Cost And Leadtime In ATE Toolings"

> Koh Tuan Meng - Micron Semiconductor Asia Lim Kok Lay - Micron Semiconductor Asia (Presented by: Steve Hamren - Micron Semiconductor)

Full Wafer Contact Burn-In and Test – The Ultimate in Parallelism?

2003 Burn-in and Test Socket Workshop March 2 - 5, 2003

> Steve Steps Aehr Test Systems

#### Agenda

- Test During Burn-in Evolution

- Burn-in Process Evolution

- Test Evolution

- Convergence Point

- Conclusions

#### **Test During Burn-in Evolution**

- Bake

- Static Burn-in (Power only)

- Dynamic Burn-in (Plus input)

- Output Monitoring Burn-in (Check some outputs)

- Burn-in and Test (Full functional test) All performed highly parallel

#### **Parallel Testing**

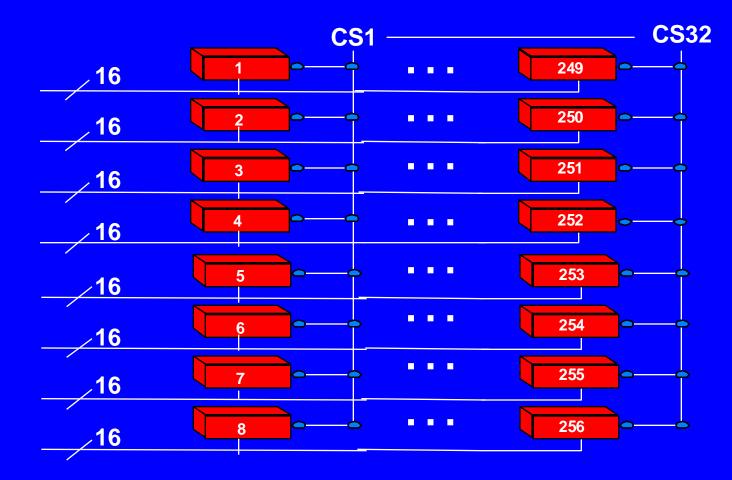

**128 Tester I/O Channels X 32 CS = 4096 Total Device I/O Pins**

BiTS 2003 Steps

#### Value of Offloading Final Test

- If the burn-in system can perform a given test, it can be much cheaper

- Opportunity to perform tests at the same time as burn-in

- Experience has shown as much as 80% of final test time can be performed during burn-in

#### **Traditional Test Process**

|            | 1                                     |  |

|------------|---------------------------------------|--|

|            | · · · · · · · · · · · · · · · · · · · |  |

|            |                                       |  |

|            |                                       |  |

| UPPRO      |                                       |  |

| <b>.</b> 🥥 |                                       |  |

| 4 K        |                                       |  |

Pre Burn-in Test - DC Parametrics Test

- Gross Functional Test Monitored Burn-in

- Dynamic Stressing

- Long Functional Test

**Final Test**

- DC Parametrics Test

- AC Parametrics Test

- Speed Sort

- Pattern Sensitivity Tests

- Long Cycle Time Tests

- Data Retention Tests

- Refresh Tests

#### **Parallel Test During Burn-in**

|        | 1              |  |

|--------|----------------|--|

| TIME   | and a first of |  |

|        |                |  |

|        |                |  |

| Uniego |                |  |

|        |                |  |

| 4 8    |                |  |

- Pre Burn-in Test - DC Parametrics Test

- Gross Functional Test

#### **Massively Parallel Test**

- Dynamic Stressing

- Long Functional Test

- Pattern Sensitivity Tests

- Long Cycle Time Tests

- Data Retention Tests

- Refresh Tests

#### **Final Test**

- DC Parametrics Test

- AC Parametrics Test

- Speed Sort

**Test Offload**

#### **Burn-in Process Evolution**

- Assembly/System

- Packaged part

- Bare die

• Full Wafer

BiTS 2003 Steps

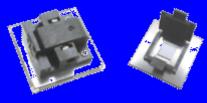

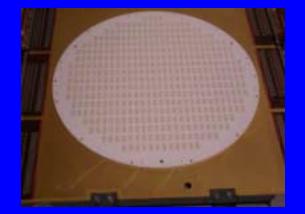

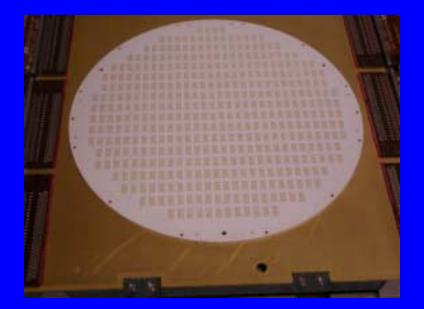

#### Wafer-Level Burn-In and Test

**BiTS 2003 Steps**

• Full Wafer Contact

• Full functional test capability

Thermal Stress

Chamber

9

#### **Progression To Wafer-Level**

- Reduce repair cost of burn-in fallout

- More critical if assembly non-repairable

- Reduce excessive burn-in

- Reduce wasted packaging/assembly

- Faster feedback to front-end

- KGD for SIP, MCM, etc. requires either bare die or wafer-level burn-in

#### **Test Evolution – External Test**

#### Full I/O speed

- Cost per channel very high (\$Ks/channel)

- Signal cable must be very short

- GHz testing very difficult

- Full I/O width

- One channel per device pin

- Total device count per test very limited

#### **Test Evolution – Structural Test**

- Typically scan chain based

- External data clock speed requirements vastly reduced

- On chip ATPG

- I/O width significantly reduced (compressed)

- Still can have edge timing constraints

- Logic BIST

- Device pin I/O speed << Test speed</p>

- Very narrow I/O (e.g., 5 pin IEEE 1149.1)

- Lower cost channels possible (~\$100/channel)

- Paralleling devices on channels possible (<\$5/device I/O)</li>

#### Wafer-Level Burn-in with BIST

#### Logical convergence of:

- Test During Burn-in Evolution (Full functional)

- Burn-in Process Evolution (Wafer-level)

- Test Evolution (Logic BIST)

- Key enabling technologies:

- Full wafer contact

- Massively parallel testing

- Logic BIST

#### Wafer-Level Logic Test, no BIST

#### Using 4 site tester:

For 300 die wafer, about 80 Test cycles

BiTS 2003 Steps

#### Wafer-Level Logic Test, BIST

#### Conclusion

- Wafer-Level burn-in and test using BIST is next step in evolution for test during burn-in

- Higher percentage of test can be performed during burn-in and thus offloaded from high speed final test

# Strategic Use of Burn In

#### 2003 Burn-in and Test Socket Workshop March 2 - 5, 2003

Tamas Kerekes ELES Semiconductor Equipment

#### Agenda

Pressure on the Burn-In

Possibility of Adding Values

Technical Solutions for Doing this

Case Studies

#### **Pressure on the Burn-In**

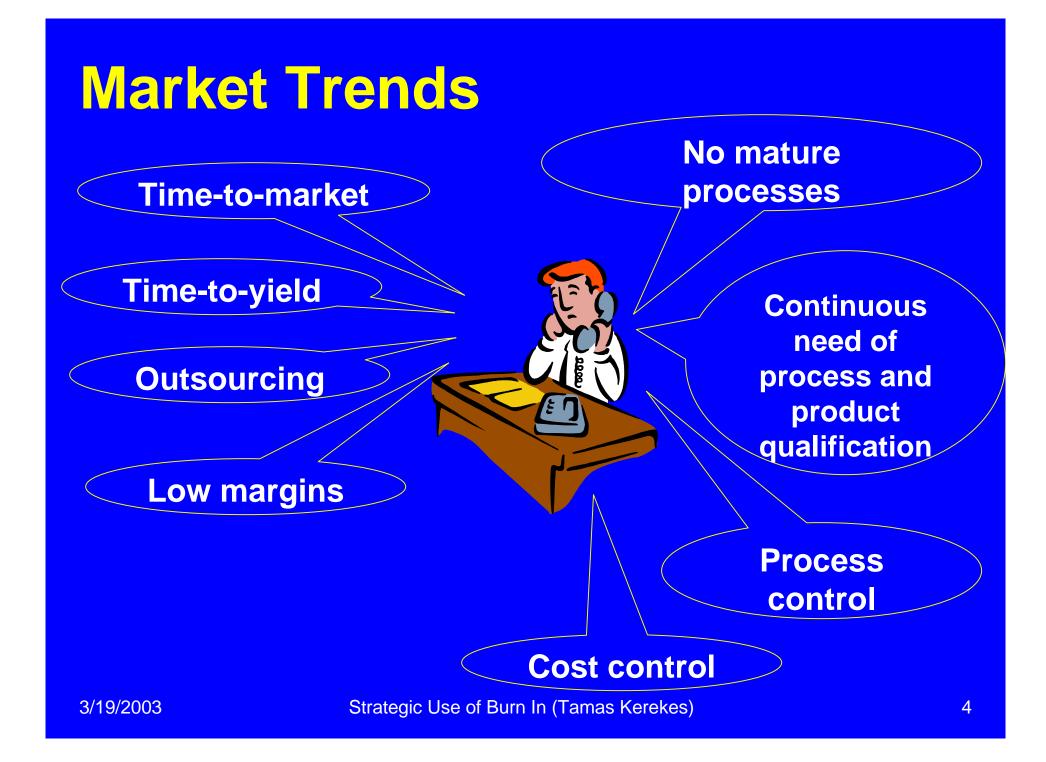

## **Technology Trends**

- Low geometry

- High transistor count

- Integration, system-on-chip, analog behavior

- New packages

- Low voltage, high power

- Non-deterministic timing

- High IO count

- Critical reliability

- Expensive sockets

- Multi-layer, fine-pitch boards

- Thermal control

- High performance electronics

- Need of qualified engineering

Strategic Use of Burn In (Tamas Kerekes)

# Keeping pace with the Moore law requires huge R&D and engineering

... and ...

it costs !

3/19/2003

Strategic Use of Burn In (Tamas Kerekes)

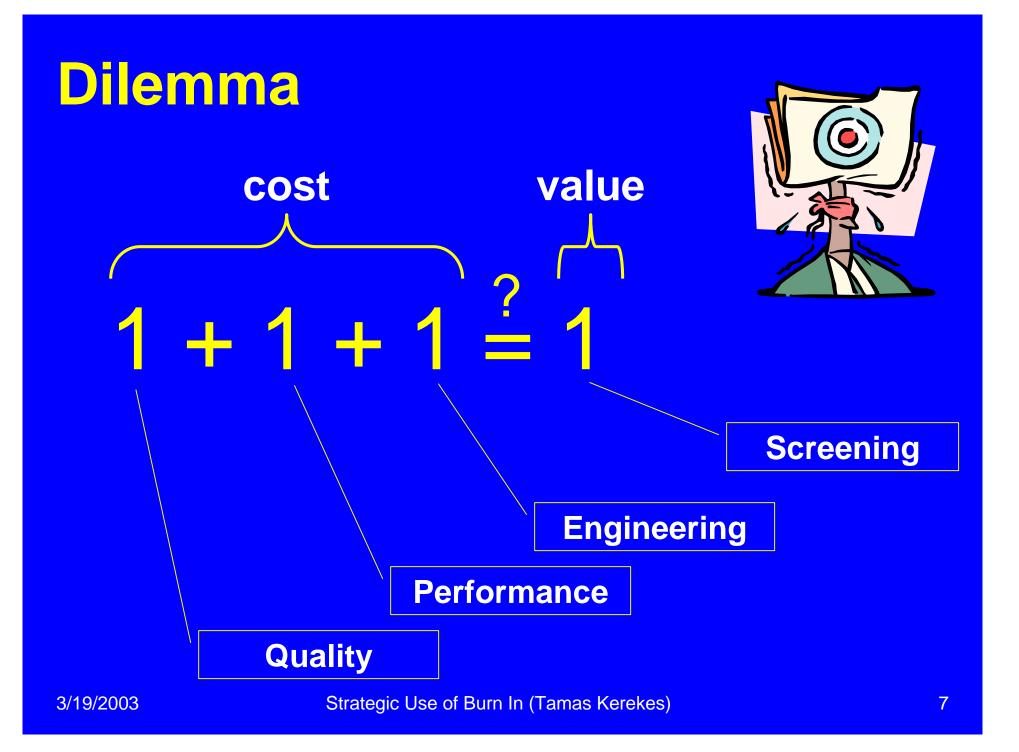

Costs and complexity are strictly related to the elementary function of the burn-in:

# ... thus there is no easy way to reduce or avoid these expenses

3/19/2003

2,7

Sil

Strategic Use of Burn In (Tamas Kerekes)

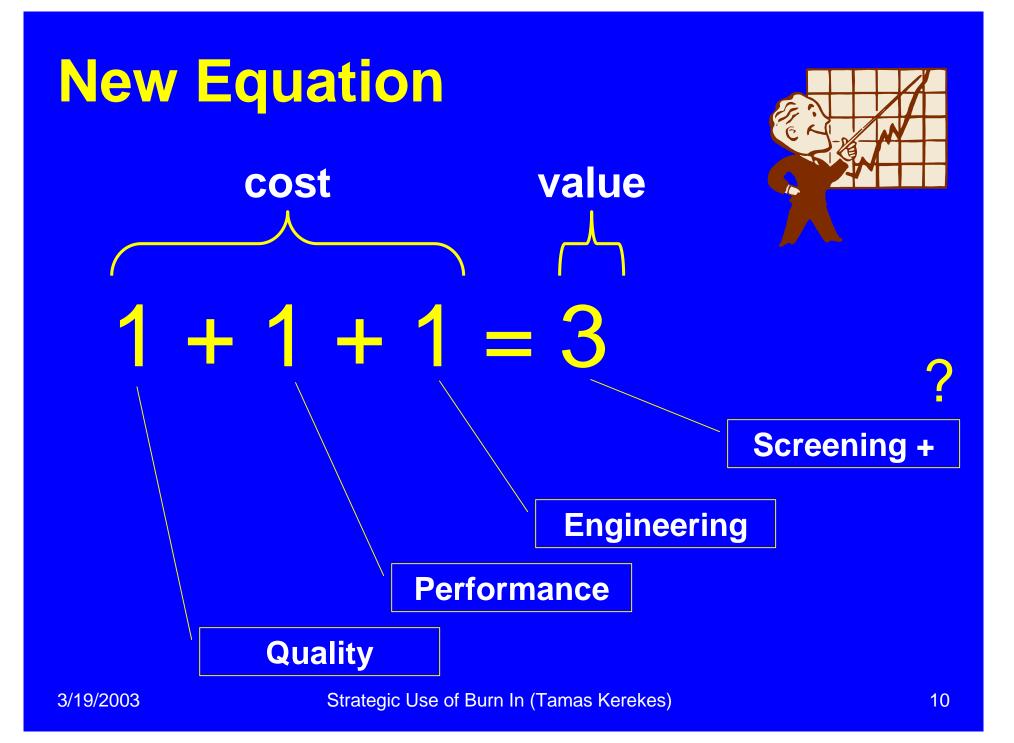

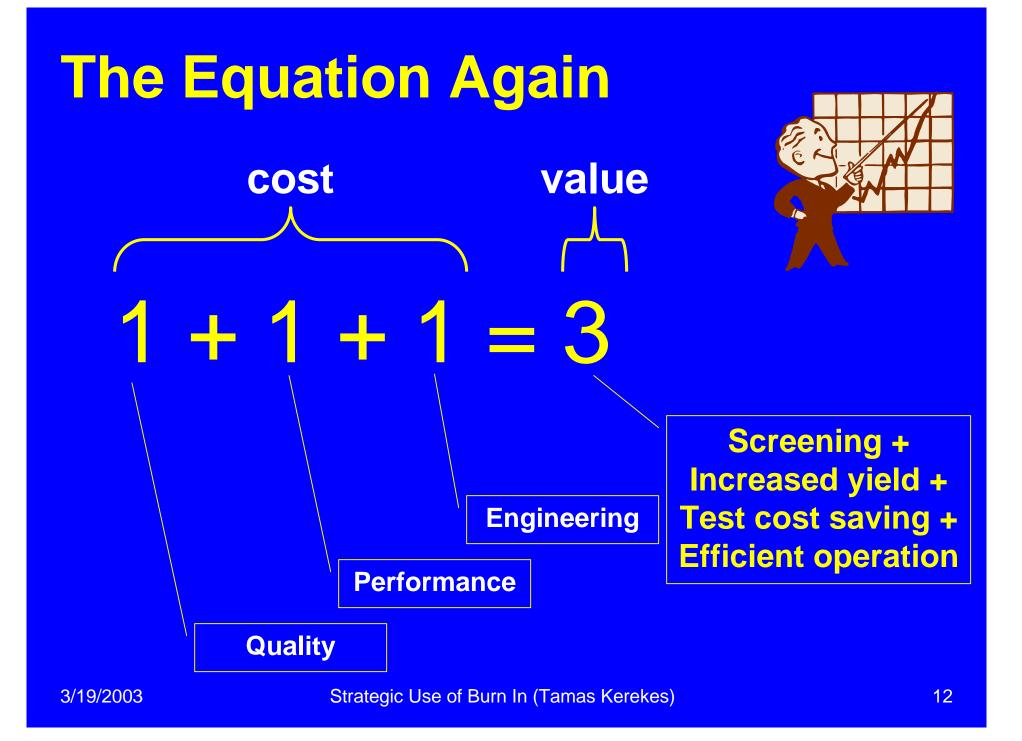

## Increasing the Value of Burn-In

## **Possible Added Values**

- Yield increase

- Test time saving

- Efficient management of the burn-in area

#### **Yield Increase**

During ramp-up (time-to-yield)

During manufacturing cycle (process control)

#### Requires:

Detailed on-line reliability data generation

- Real-time data processing

- Automated feedback of the data

## **Test Cost Saving**

Manufacturing - Goals

Reduced test-time on ATE

Better quality control in the production cycle

- Operations

- TDBI (full burn-in)

- Batch Testing (when no burn-in is required)

- Qualification

- Replacement of the intermittent test on ATE with continuous in-line testing

- Not only for memories

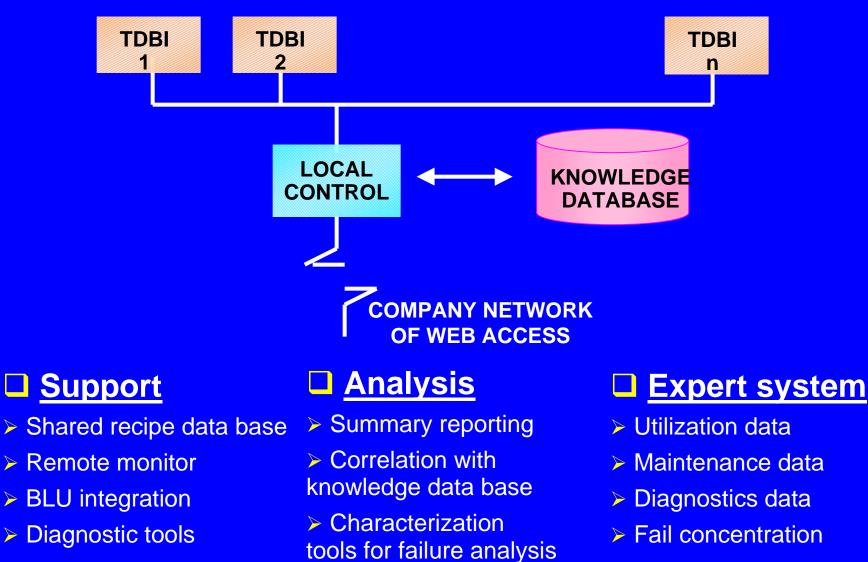

#### Area Management Statistical Process Control Utilization tracking Maintenance tracking Defect analysis Area Control Lot tracking Scheduling Integration Expert System "tell the operator what to do"

#### **Technical Solutions**

# Key Factors Equipment Data management Organization and methodologies

# Equipment

Full use of DFT methodologies, for increased visibility Scan, JTAG, SoftBIST, … Coverage of a wide range of devices (in the same chip) Analog, digital, memory Flexible, programmable test flow Functional tests Characterizations (smoo, bitmap, ...) Flexible, programmable data generation

# **Flexible Device Management**

Device specific algorithms (not only flat vectors) run on the tester electronics and on the device under test

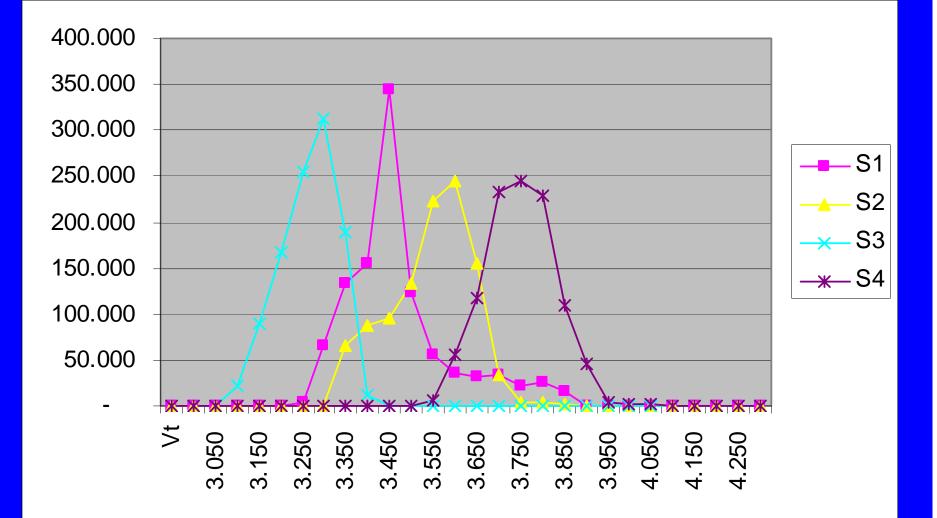

# **Example: Bitmap**

3/19/2003

## **Example: Distribution**

3/19/2003

# **Data Collection System**

3/19/2003

# **Development Tools**

#### **SPECIFICATIONS**

#### **APPLICATION**

Vector translation and IO assignment (simple case)

Device specific algorithms (C) and test flow description (scripting)

GUI for automated script generation

3/19/2003 Strategic Use of Burn In (Tamas Kerekes)

23

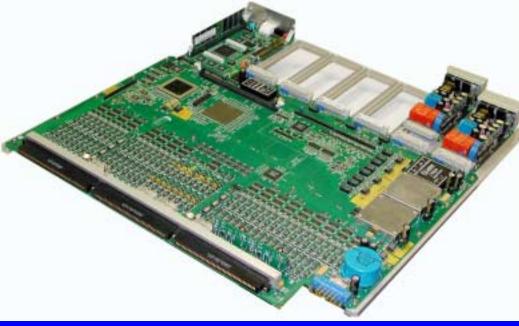

## **ART 200**

- Flexible hardware and software structure

- High electrical performance

- Standard and user specific algorithms

- Scripting language for test flow

- Data collection and processing tools

- Area management support

## **Case Studies**

# Case Study 1: High Coverage Qualification

| Standard                                             |                  | "Strategic" |

|------------------------------------------------------|------------------|-------------|

| 69%                                                  | % of die covered | 92%         |

| 100                                                  | stress factor    | 141         |

| ATE                                                  | data generation  | BI + ATE    |

|                                                      |                  |             |

| 55 days                                              | cycle time       | 45 days     |

| 3/19/2003 Strategic Use of Burn In (Tamas Kerekes) 2 |                  |             |

# Case Study 2: New Embedded NVM Process

Same tools used for characterization, qualification and production quality control

Yield ramp-up from 7% to 95% in 1 WK using characterization data generated in production

# Case Study 3: TDBI on Embedded NVM

Embedded NVM tested only during burn-in

Test result correlation proven

Fully integrated burn-in area

ATE test time and ATE investment reduced by 60% (6 M\$)

Total process cost reduced by 40%

## Case Study 4: **Fully Parallel Test on Flash** 64 Mbit TSOP56 All functional test steps implemented in a parallel test ("burn-in like") environment, as an additional process step ATE runs only DC and AC tests (85% test) time saving) Total process cost reduced by 50% Increased outgoing reliability (cycling) "gratis"), value not measured yet

# thank you

# for your time and consideration

3/19/2003

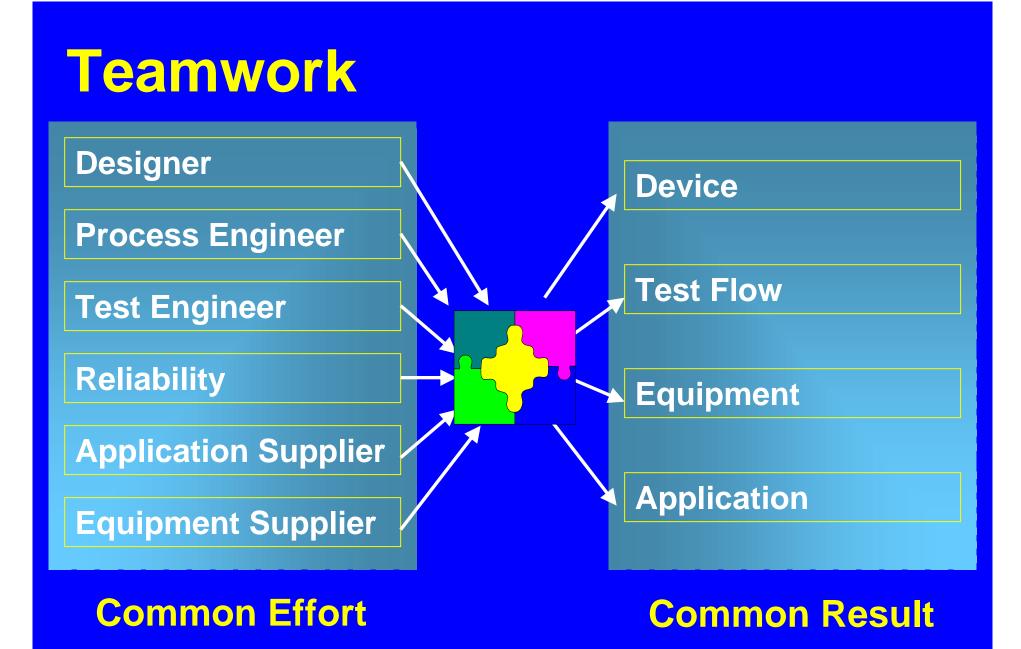

A FLEXIBLE ELECTRICAL INTERFACE DESIGN FOR THE FIXTURE BETWEEN TESTER AND DUT TO ACHIEVE REDUCED COST AND LEADTIME IN ATE TOOLINGS

## 2003 Burn-in and Test Socket Workshop March 2 - 5, 2003

Koh Tuan Meng Lim Kok Lay Micron<sup>-</sup>

## Agenda

- Background

- Objectives

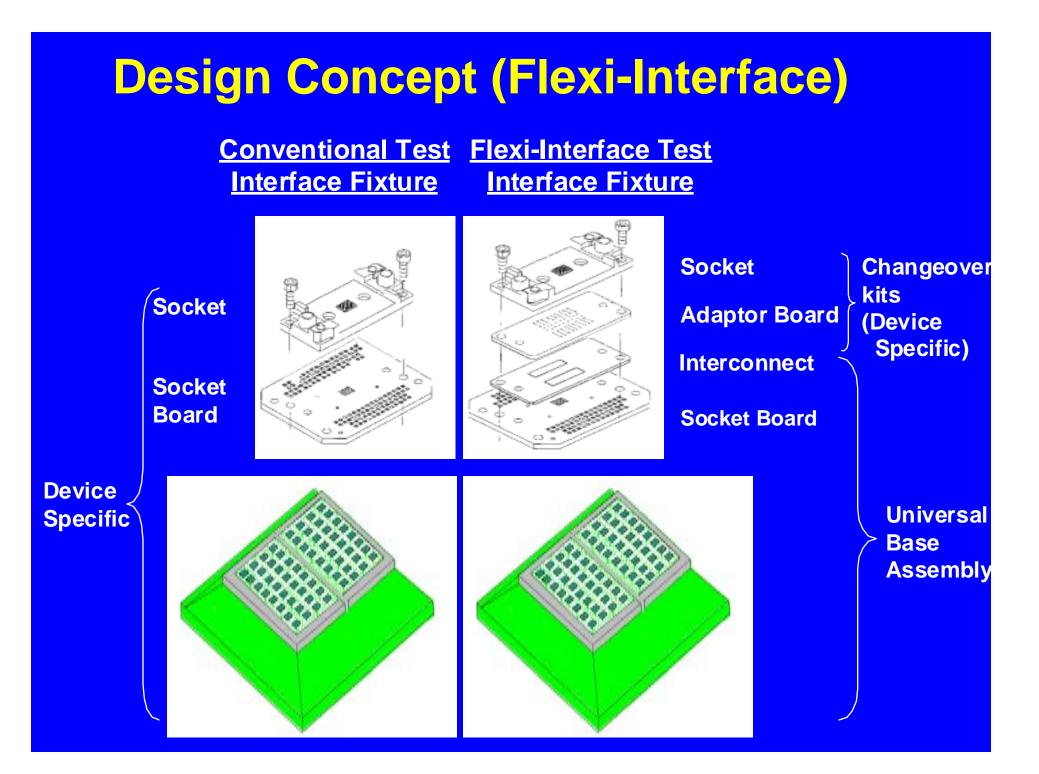

- Design Concept (Flexi-Interface)

- Prototype Evaluations Data

- Conclusions

#### Background

- Device Specific Electrical Inteface

- Tester channels routed to DUT (device under test) according to device pinouts.

- No flexibility in toolings.

- High Toolings Cost

- Existing toolings cannot be used if device pinouts are different.

Long Leadtime For Toolings

Tpyical cycle time for building a new electrical interface is about 2 to 3 months.

## **Objectives**

- To have better toolings flexibility

- Reduce Test toolings cost.

- Reduce Test toolings leadtime.

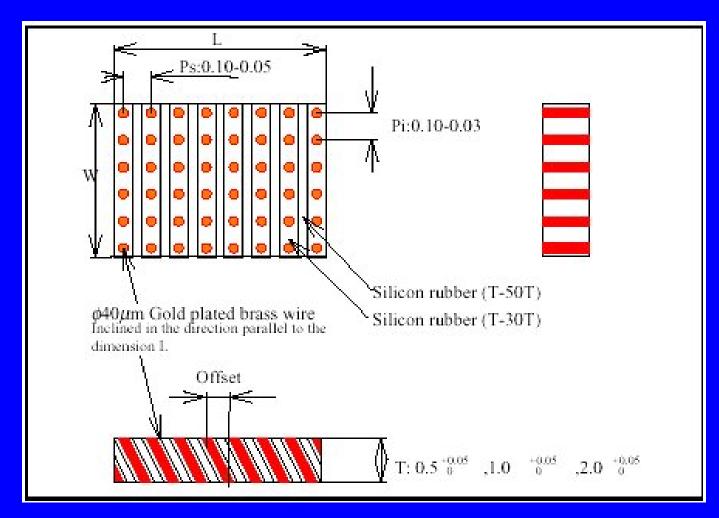

## **Interconnect Material**

#### **Shin-Etsu Interconnector (SMM)**

#### Courtesy of SHIN-ETSU (http://www.shinpoly.com)

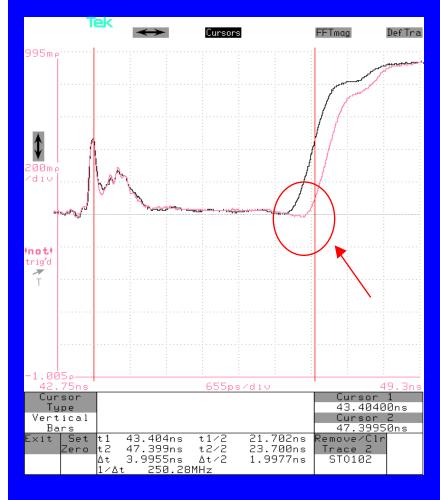

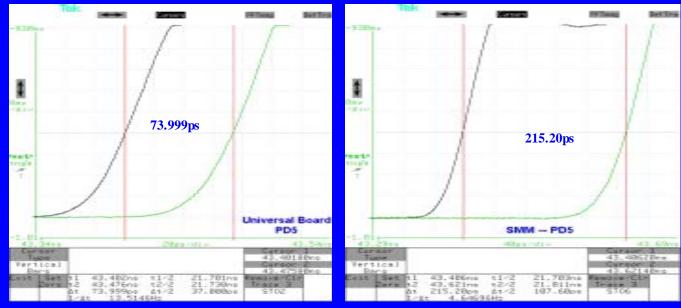

#### **Time-Domain Measurements**

TDR (Time Domain Reflectometry) measurements were taken to capture any abnormalities on the impedance profiles for the complete signal path.

The impedance dips below 50ohms at the portion of the SMM interconnect. The SMM interconnect is not impedance control and hence causes some impedance mismatch (it has a capacitive effect).

#### **Time-Domain Measurements**

TDT (Time Domain Transmission) measurements were taken on the bare boards to derive the actual propagation delay introduced by the SMM interconnect.

The delay is only about 9ps.

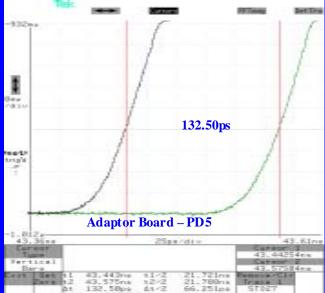

#### **Frequency-Domain Measurements**

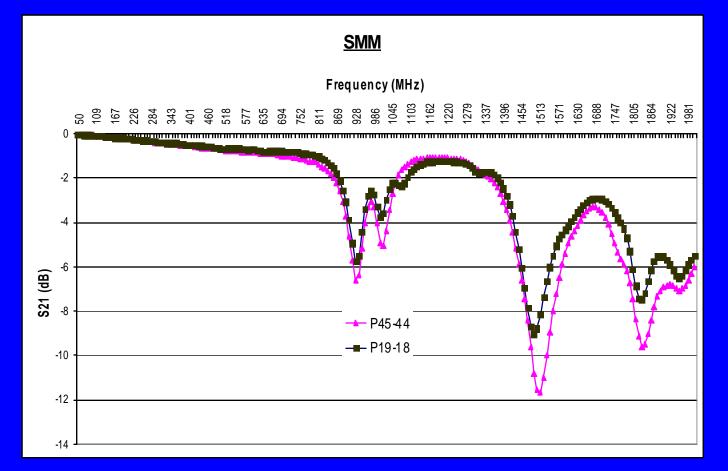

Insertion Loss measurements were taken on the bare boards to check for the signal degradation caused by the SMM interconnect.

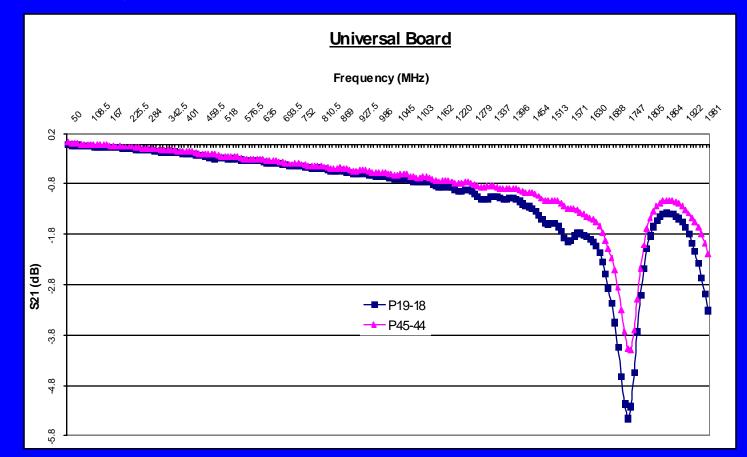

#### **Frequency-Domain Measurements**

Adaptor Board

#### **Frequency-Domain Measurements**

The frequency bandwidth for the complete assembly drops to 700MHz (@ 1dB insertion loss).

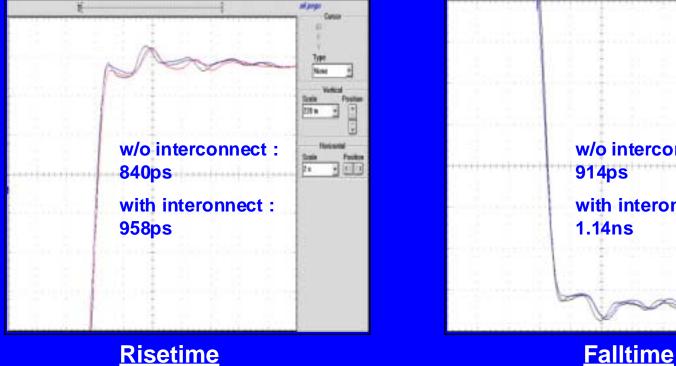

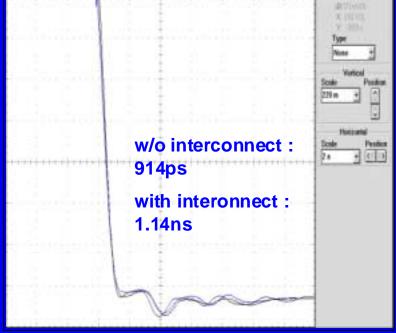

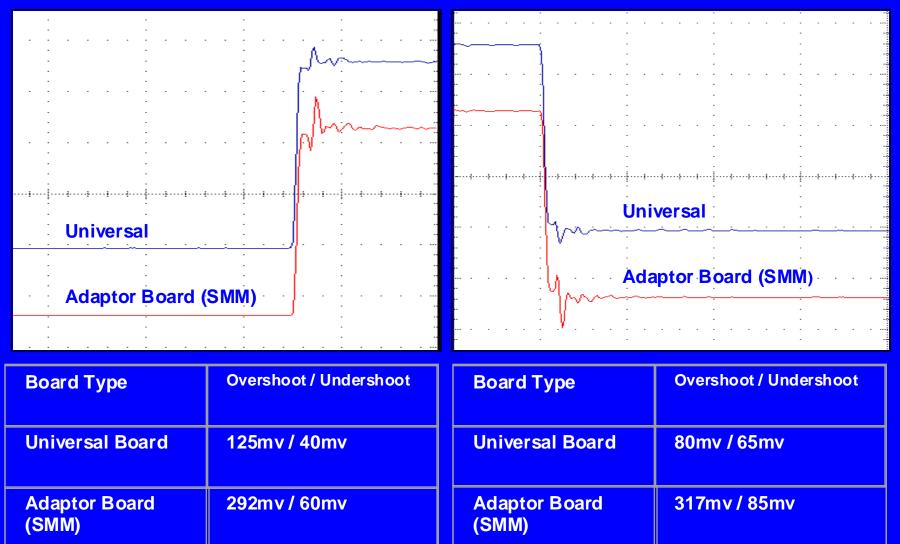

A short program was developed on the ATE tester to check for the rise time, cross-talk, overshoot and undershoot performance of the flexible electrical interface.

With the interconnect, the risetime is degraded by about 100ps.

#### **Crosstalk Measurements**

The interconnect causes about 10% overshoot voltage.

#### Conclusions

- With the data collected in both the Time & Frequency domains, the flexible electrical interface concept has been proven to be viable for device testing (for SDRAM). There is, however, still room for improvements on the interface between board to board.

- The next challenge would be to prove out the Flexi-interface concept for higher speed device testings (DDR II & beyond).