Burn-in & Test Socket Workshop 2000

# **Session 4b**

# Test Sockets / Contactors

BURN-IN & TEST SOCKET WORKSHOP

#### <u>COPYRIGHT NOTICE</u>

• The papers in this publication comprise the proceedings of the 2000 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, or the Institute of Electrical and Electronic Engineers, Inc.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, proper acknowledgement should be made to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

# **Presentations**

#### "Evaluation Of Test Socket For TSOPII Package"

Peng Ching Ho Micron Semiconductor

# **"Critical Performance Characteristics For High Frequency Test Contactors "**

John O'Sullivan Johnstech International

#### "Design Characteristics Of Test Contactor And ESD Concerns"

Jit Cheh Tan Intel Tark Wooi Fong Intel

# Evaluation of Test Socket for TSOPII Package

**2000 Burn-in and Test Sockets Workshop**

HO, Peng Ching Micron Semiconductor Asia Singapore

### Agenda

- Background

- Requirement

- Evaluation Criteria

- Non Electrical

- Electrical

- Reliability

- Conclusions

### Background

- Low socket life span

- only spec to 10K test insertions

- show rising trend of continuity fallout if operated

>10K test insertions

- Not cost effective

- socket cost \$45 each

- 64 test sites per system

- Low speed testing capability

- only spec to <200 MHz</p>

### Requirement

- 100% "Plug-n-Play" solution

- eliminate any mod. To handler changekit or socket board design

- reduce unnecessary tooling cost \$\$\$

- High socket life span

- Cost effective

- performance-cost index

- High speed testing capability

#### **Socket specifications**

|                               | Original<br><u>socket</u> | Socket<br><u>under eval.</u> |

|-------------------------------|---------------------------|------------------------------|

|                               |                           |                              |

| Cost                          | <b>1</b> x                | <b>0.25</b> x                |

| (per insertions)              |                           |                              |

| <ul> <li>Life span</li> </ul> | 10k                       | 200k                         |

| (max insertions)              |                           |                              |

| <ul> <li>Bandpass</li> </ul>  | 200Mhz                    | 800Mhz                       |

# **Evaluation criteria (non-electrical)**

- Handler jam rate

- at tri-temp. (hi-temp. ambient, cold-temp.)

- specs : 0 jam / 3000 units

- Device damage I

- visual mechanical inspection (after 4 insertions)

- in-house VM criteria

- specs : 0 defects / 1000 units

- Device damage II

- solderability test (after 4 insertions)

- in-house criteria

- specs : 0 defects / 32 units

### **Evaluation criteria (electrical)**

- Contact resistance check

- tester-handler interface

- specs : < 5 ohm</p>

- Leakage check

- tester-handler interface

- specs : < 200 nA at 5V</p>

- ESD check

- use electrostatic fieldmeter

- specs : < 500V</p>

# Evaluation criteria (electrical)

- Signal characteristics

- overshoot/undershoot

- rise/fall time

- Jittering

- Signal distortion

- Parasitic component measurement

#### **Signal characteristics**

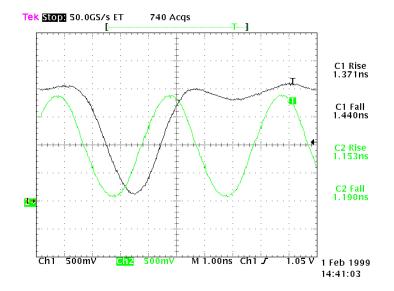

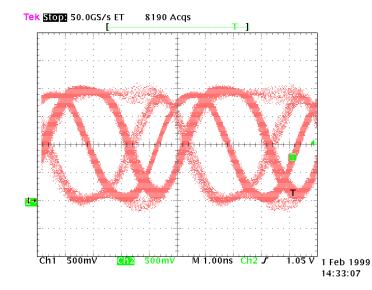

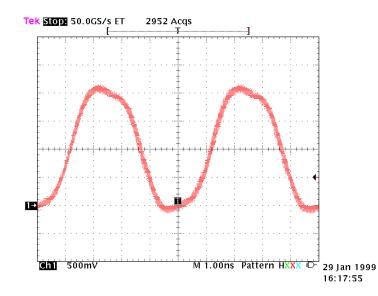

#### At 200 MHz

**Socket under evaluation**

(no significant improvement)

#### **Original socket**

#### **Signal characteristics**

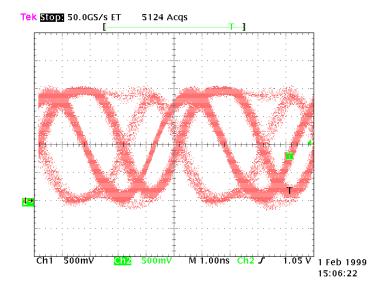

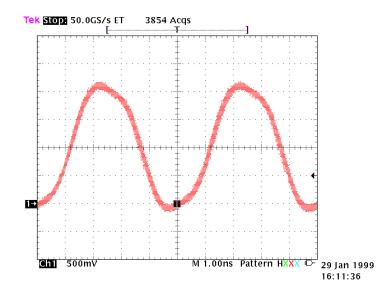

#### At 250 MHz

#### Socket under evaluation

(no significant improvement)

#### **Original socket**

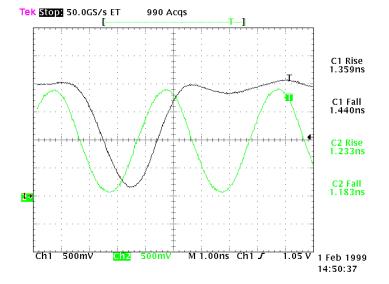

# **Jittering**

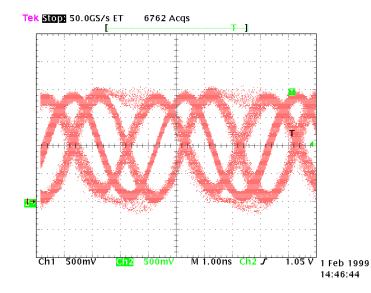

#### At 200 MHz

#### Socket under evaluation

(no significant improvement)

#### **Original socket**

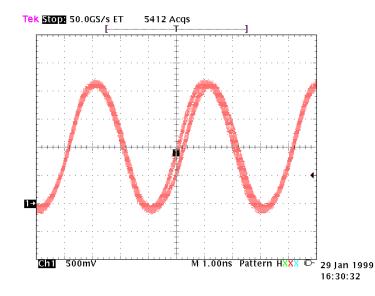

# **Jittering**

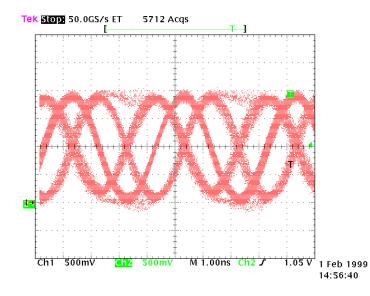

#### At 250 MHz

#### **Original socket**

#### **Socket under evaluation**

(no significant improvement)

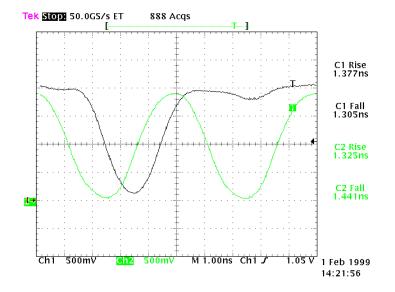

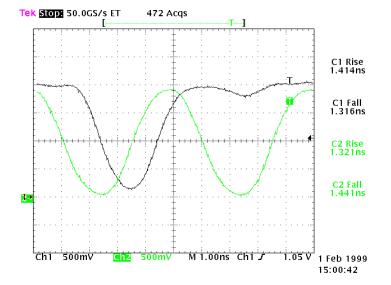

### **Signal distortion**

#### At 200 MHz

**Original socket**

#### **Socket under evaluation**

(no significant improvement)

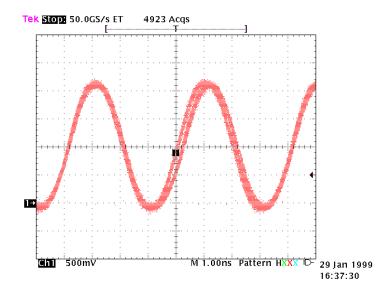

### **Signal distortion**

#### At 250 MHz

**Original socket**

#### **Socket under evaluation**

(no significant improvement)

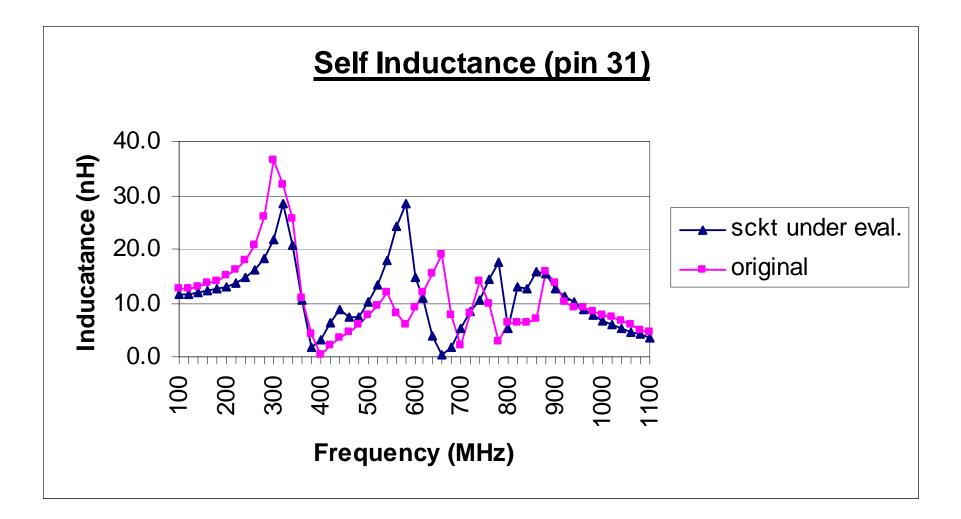

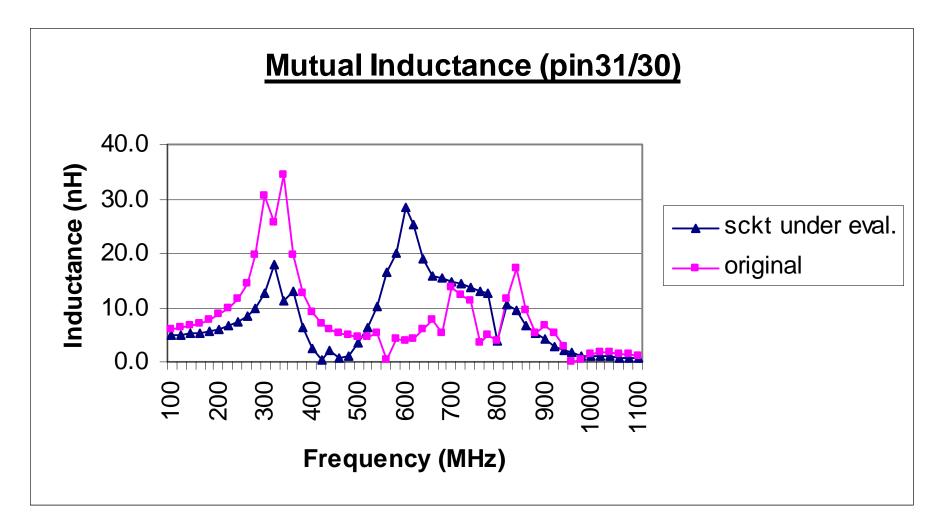

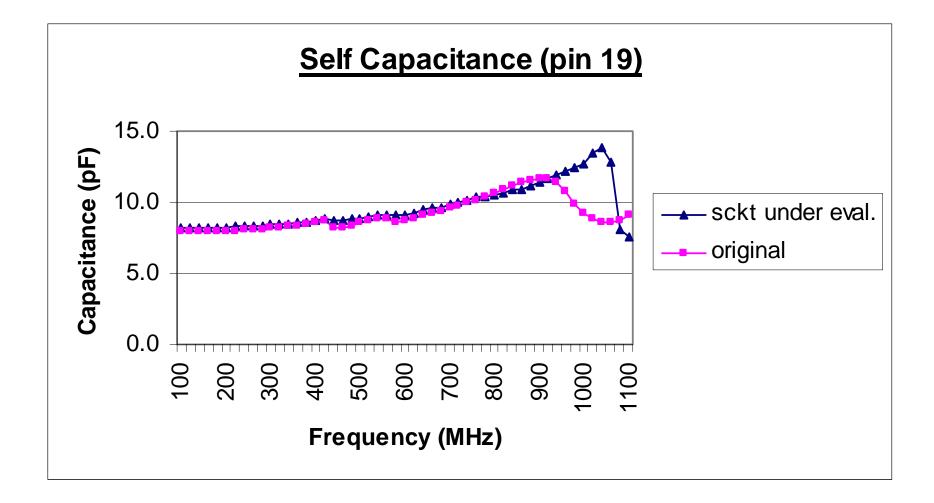

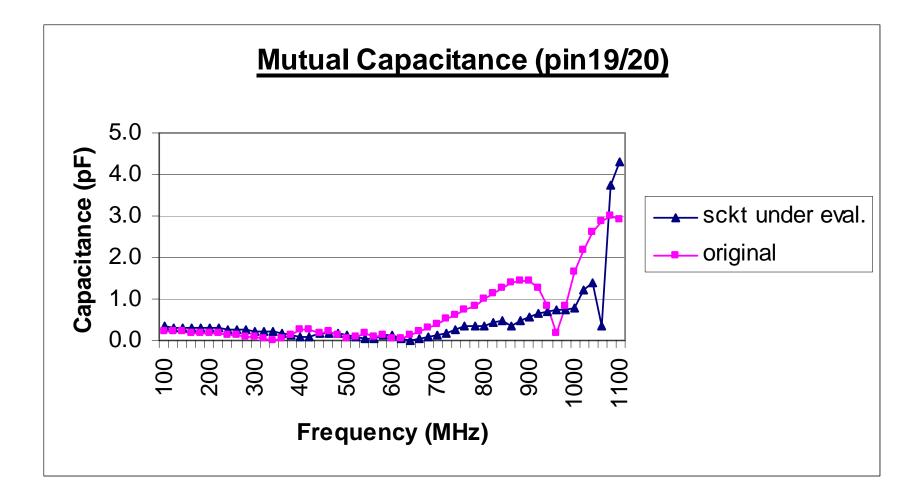

| Parameter          | <b>Original Socket</b> | Socket under Eval. |

|--------------------|------------------------|--------------------|

| 1) Cs @200MHz      | 8.0 pF                 | 8.3 pF             |

| 2) Cm @200MHz      | 0.2 pF                 | 0.3 pF             |

| 3) Ls @200MHz      | 15.0 nH                | 13.0 nH            |

| 4) Lm @200MHz      | 8.6 nH                 | 6.0 nH             |

| 5) Xtalk (derived) | 0.15                   | 0.13               |

| 6) Passband        | >800 MHz               | >800 MHz           |

# **Evaluation criteria (reliability)**

- Contact Consistency check

- lot size : 1000 units

- test temperature : hi-temp

- spec : <1% continuity fallout</p>

- Volume checkout

- verify against specified socket life span

## Conclusions

- Sourcing socket based on manufacturer's specification is high risk and may lead to high cost impact.

- In this particular evaluation, if socket change is pursed the cost incurred will be unnecessary as we see no advantage to use the alternate socket.

- Important to assess the socket performance in the actual operating environment rather through datasheet

### Conclusions

cont'd ....

- This risk can be significantly reduced if we performed the suggested checkouts grouped under :

- Mechanical (non-electrical) performance

- Electrical performance

- Reliability

- Socket performance is ONLY part of the entire tester-handler interface.

# Critical Performance Characteristics for High Frequency Test Contactors

John W. O'Sullivan Product Manager Johnstech International February 27-29, 2000

BURN-IN & TEST SOCKET WORKSHOP

Johnstech International

SOCKET WORKSHOP

#### Critical Factors of Test Contacting

- Reliability: Dependable performance

- <u>Repeatability</u>: Successful similar results each and every time

- <u>Resolution</u>: Measurable incremental differences

BURN-IN & TEST SOCKET WORKSHOP

#### Test System Issues for Poor OEE

- Test system components leave significant room for error

- Lower First Pass Yields

- Decreased Throughput

- System Jams

- Overall Inefficient Setup

BURN-IN & TEST SOCKET WORKSHOP

#### Test System Harmony Increases OEE

- Today's high frequency device testing requires a collaborative effort on the part of the various test system components

- Handler

- Tester

- Load Board

- Test Contactor

Johnstech International

- Loose alignment systems do not offer a high probability of success

- The more loose a system, the higher the probability of failure

- Poor alignment or calibration of device lead-to-contact can cause component leads to become lodged between contacts

Johnstech International

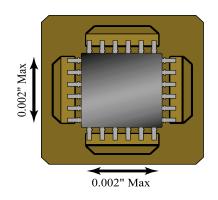

Allowable Device Movement

BURN-IN & TEST SOCKET WORKSHOP

Critical Factors for Package Dimensions

Johnstech International

#### Considering the probability of contacting

- as devices continue to get smaller, lead spacing is getting smaller

- leads per device continue to increase

7

BURN-IN & TEST SOCKET WORKSHOP

- Wide alignment pattern reliability results include a "no lead-to-contact continuity" condition

- If there is sufficient correction in the course of travel of the device leads to the contacts in the contactor:

- Statistical random factors are reduced

- Probability of reliable operation is increased

- Not enough over travel is a high resistance, low reliability electromechanical connection

- High resistance interconnect starves parts of current flow, which can cause parts that are marginally good to fail in test

Johnstech International

9

Short Rigid Contact Example

# Reliability

- The probability of a highly reliable interconnect is determined by the alignment control and control of over travel with the hard stops

- It is the controlling action of the hard stop that reproduces the travel of each device inserted into the contactor

BURN-IN & TEST SOCKET WORKSHOP

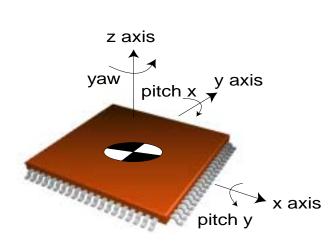

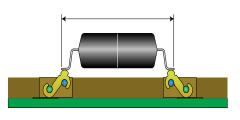

Package pitch and yaw illustration

# Repeatability

- Package presentation is the pitch and yaw that occurs when contacts and leads do not mate properly

- With a loose system, there can be insertion pitch and yaw

- Pitch and yaw has a negative impact on the lead of the device mating with the contacts of the test contactor

BURN-IN & TEST SOCKET WORKSHOP

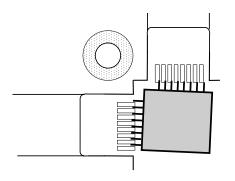

# Repeatability

If the device leads are improperly positioned with the contacts in the test contactor, you can't test the package

Improperly Positioned Leads

BURN-IN & TEST SOCKET WORKSHOP

Johnstech International

12

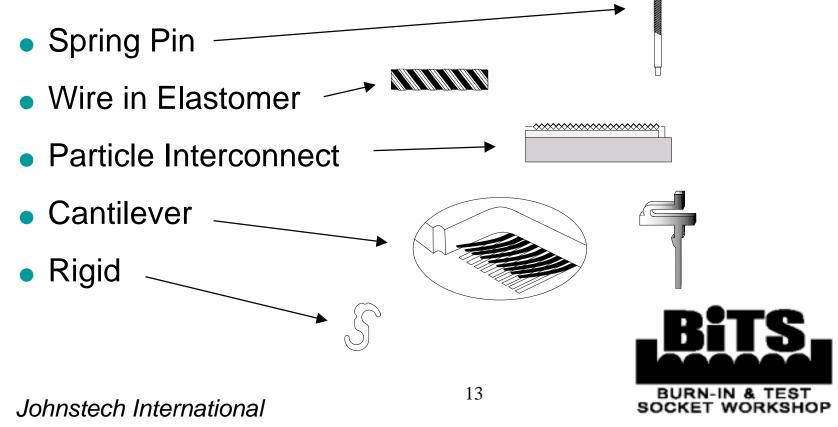

# Repeatability

Contacting methods that are factors in deciding the value of electrical and mechanical repeatability include:

## Repeatability

The elastomeric element repeatedly returns the contact tip to its original height while maintaining its spring force even after hundreds of thousands of device insertions

Side View

Front View

Short Rigid Contact Mechanical Dynamics

BITS.

ET WORKSHOP

Johnstech International

14

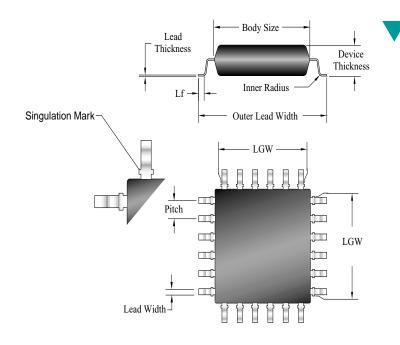

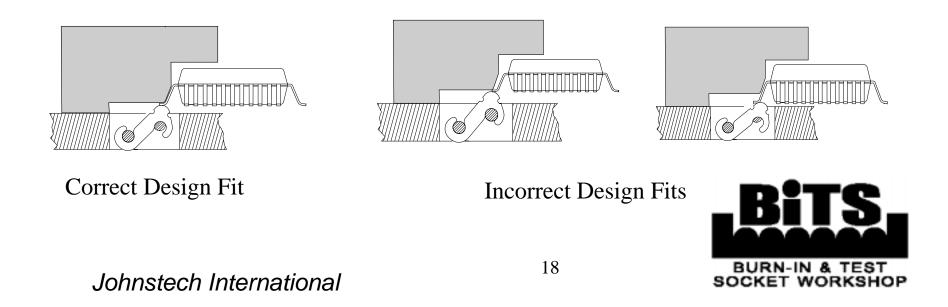

- Device package configuration is designed to an industry standard

- Actual product produced resolves to a smaller range of manufacturing increments

- Package dimensions may fall anywhere between the high or low end of industry specification

BURN-IN & TEST SOCKET WORKSHOP

- Generic contactors align to nominal dimensions

- This is a "one size fits all" design philosophy

- Designing to nominal values can provide either too much correction or too little correction

- One of the primary concerns contactor companies have is change to "trim and form" of the package

BURN-IN & TEST SOCKET WORKSHOP

- Packages larger than the nominal are a tight fit in any contactor

- The impact is lead bending and contact mashing, with automated material handlers jamming

- Packages smaller than the nominal are a loose fit in any contactor

- The impact is improper placement of the package in the contactor, as well as loss of electrical continuity

17

The end result can reduce test socket life, and cause a significant reduction in overall equipment effectiveness

BURN-IN & TEST SOCKET WORKSHOP

Johnstech International

- Correction is developed through the use of alignment plates, hard stops and leadbackers

- The finer the resolution of the alignment mechanism relative to the package and device leads, the greater the repeatability

# Conclusion

- Test Reliability is having a certain confidence level in the contacting solution's ability to deliver the desired results as part of the overall test system

- Test Repeatability is inherent in the design of the contactor components and controlled through the interaction of the components with the handler and device under test

- Test Resolution is becoming increasingly more critical as device size decreases, the space between leads decrease, and the number of leads per device increases

Johnstech International

# Conclusion

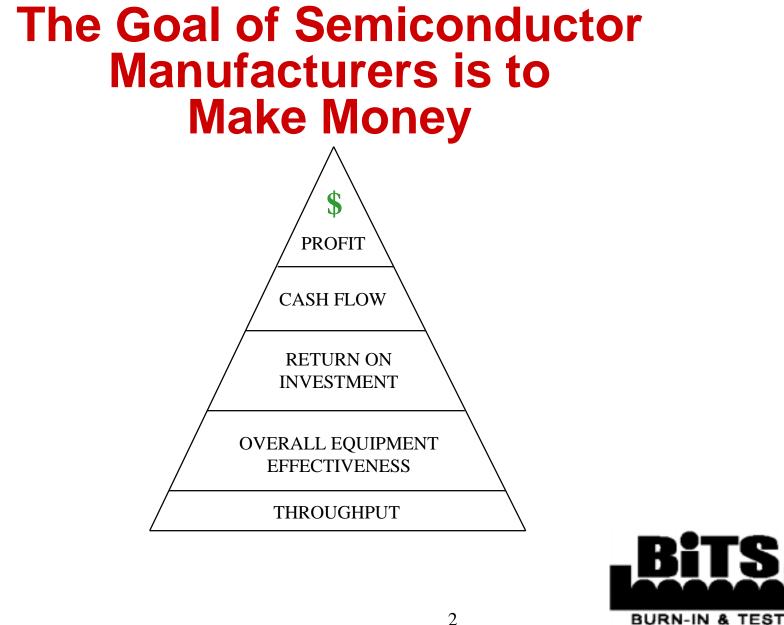

- Semiconductor manufacturers are in business to make money

- Test engineers must work with all of their test system component suppliers

- Continuous improvement in overall equipment effectiveness (OEE) is the goal

BURN-IN & TEST SOCKET WORKSHOP

# Design Characteristics of Test Contactor & ESD Concerns

## By JC Tan & TW Fong Intel Technology Sdn. Bhd Intel Test Tooling Operation (ITTO) Malaysia

JC Tan Feb 2000

Intel Itto Penang

## Agenda:

- > Presentation objectives

- Introduction

- Design Considerations

- Decision drivers and common issues

- ESD considerations

- Methods to minimize ESD

- Conclusions

## **Presentation objectives**

To discuss test contactor design considerations and its impact on cost management

> To share some ESD concerns on test contactor design

## Introduction:

## **Types of Test Contactors**

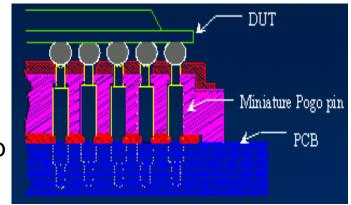

- ≻Pogo Pin

- Elastomer

- Fuzz Button

- Cantilever

- Diamond Bump

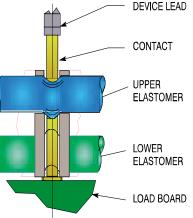

Fig 1. Pogo Pin TC

Fig 2. Diamond Bump TC

- Pogo Pin is the most commonly used

- Cost effective

- Reliable

- Flexibility

- Good Performance

# Design considerations for cost & performance

Test contactor design requirements are driven by the CPU design, as today's high performance CPU requires high power and current but lower voltage.

#### Test contactor material

- Good mechanical properties under test temperature of -55°C 150°C

- low ESD (with surface resistivity ideally within static dissipative material of 10<sup>6</sup> to 10<sup>9</sup> Ohms/Sq)

- machining tolerance of ± .001" in X-Y-Z directions (current 500-600 pins, future >1K)

- > High Strength, minimal warpage during testing (high speed test, <1sec)</p>

- Wear resistance

- Thermal stability

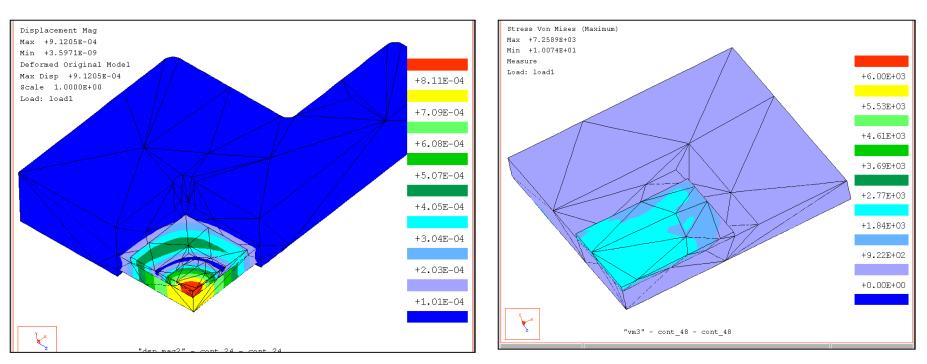

#### Example of tool to predict the performance of test contactor material

Fig 3. Displacement Vs Load

Fig 4. Stress Vs Load

#### **Design Considerations continue..**

Test contactor body design

- Single or parallel testing (multiple socketing at one time)

- Reusable parts for cost saving

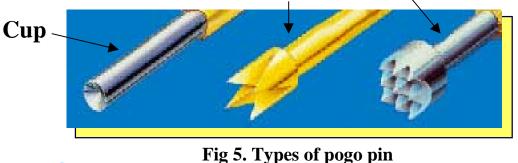

Selection of pogo pin type are based on

Performance (Freq, current, power and inductance)

Intel ITTO Penang

Cost ( custom made or industrial standard )

Serrated

- Different type of application (BGA,LGA, PGA) using different pogo pin tip (cup, crown, serrated and pencil)

- Life span

Crown

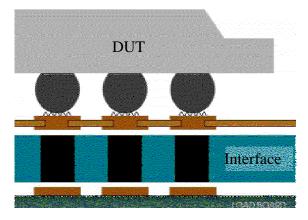

Fig 6. X-sectional view of a Socketed Package  $\frac{7}{7}$

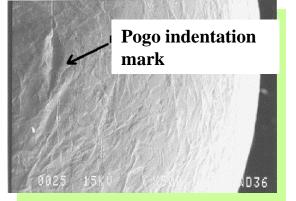

# Life span of pogo pin is determined by its resistance over extended socketing

$$R = \frac{\rho L}{A}$$

R = resistanceL = length

A = area of contact

$\rho$ = base material (low resistance and able to handle high current and temperature)

Area of contact is affected by wear resistivity (hardness) of pin plating material eg. Gold, nickel or rodium.

Resistance is also affected by contact force on pin ;  $F \propto 1/R$

## **Decision drivers & common issues**

#### Performance

- To meet product requirement (freq, inductance, power, capacitance & resistance)

- ESD considerations; lower voltage is more sensitive to ESD (discuss in second part of presentation)

- Pogo pin life span and quality

- Life span varies for different test specs, environment, temperature and contamination (solder flakes, flux and solder mask)

Fig 7.Ball damage

JCTTan Feb 2000

Fig 8.Pin damage Intel ITTO Penang

Fig 9. Inner pad damaged 9 by pogo pin

# **ESD Considerations**

#### Introduction:

As the CPU voltage is going down therefore it becomes more sensitive to ESD

- ESD event is the transfer of electrostatic charges between bodies of surfaces that are at different electrostatic potential.

- > 2 ways of static charge generation on material :

- Triboelectric charging

- Induction

- The type of charge generated is a function of the relative positions of the material on the triboelectric series (Fermi-level)

- Can remain for extended periods of time, removed only by air ionization or a grounded path.

- ESD events are insidious and could be deadly to DUT but we cannot feel it unless it is > 3500 V

- ESD can create latent failures that potentially cannot be screened out, but show up as field failures.

## Static charge generation on material

#### Triboelectric charging

- Rate of charge generation is related to intimacy of contact, coefficient of friction, rate of separation, conductivity of material and relative humidity.

- Eg.Circuit Packs As Bubble Plastic Cover Is Removed will generate 26KV, Person Walking Across Vinyl Floor 12K, Circuit Packs As Packed Foam Lined Shipping Box 21K

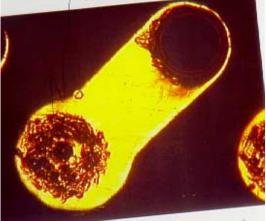

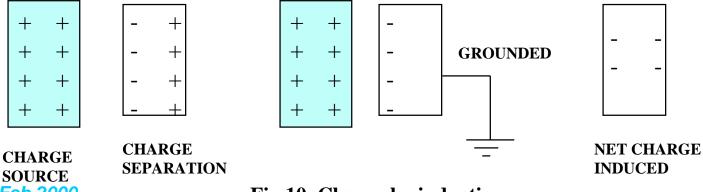

#### Charge by Induction

- Contactless method

- Electrostatic field from any charge sources will induced charge separation on conductive material if they are close enough

- Can cause field induced model failure (FIM)

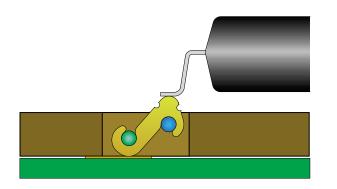

Fig 10. Charge by induction

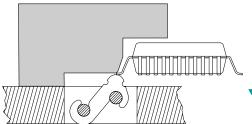

### How ESD is build up on Test Contactor

- Chuck and socket is subject to long time frictional movement and contact with the packages. (Tribocharging)

- Chuck and socket have the most intimate contact with packages during test.

- > Close distance,  $(E = Q / 4\pi \epsilon r^2)$  and conductors contact provide low resistance grounding, thus induce rapid redistribution of charges.

Metal to metal contact

Test

Contactor

Electron drain out through GND or VCC

Handler Chuck

Package

Intel ITTO Penang

Fig 11. ESD build on TC

Data from Kuek12

## Methods to minimize ESD

Some of the preventive actions are:

- Installation of ionizer in handler

- Changing device handling components materials to ESD safe material

- Changing device pick up rubber suction cup inside handler to dissipative material

- Grounding of moving parts to eliminate build up of tribo-charge

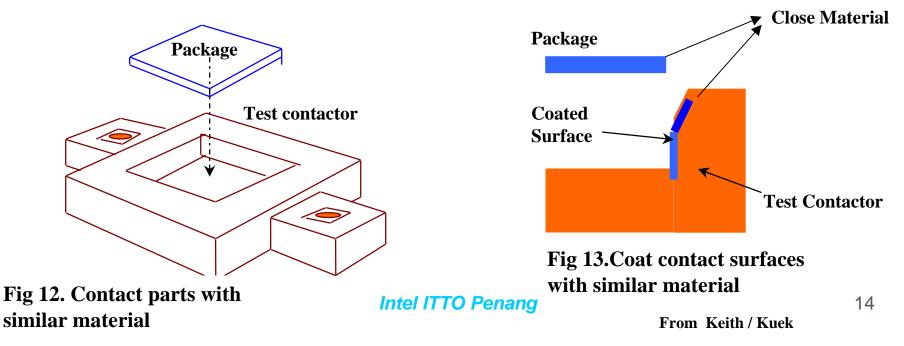

- Use of similar material for contacted parts

- Alternate methods to reduce ESD

## Alternate methods to reduce ESD in TC

#### Method 1: To Reduce Tribo-charges (limited data)

- Utilize contact material with close or similar "Fermi Energy Level".

- Match contact surfaces with similar material, technology constraint.

- Difficulties hard to find suitable materials that are similar Fermi and yet maintain good thermal, mechanical & electrical characteristics.

#### Method 2: Increase Dissipation (limited data)

- Apply dissipative material with low resistivity or metal as test contactor body.

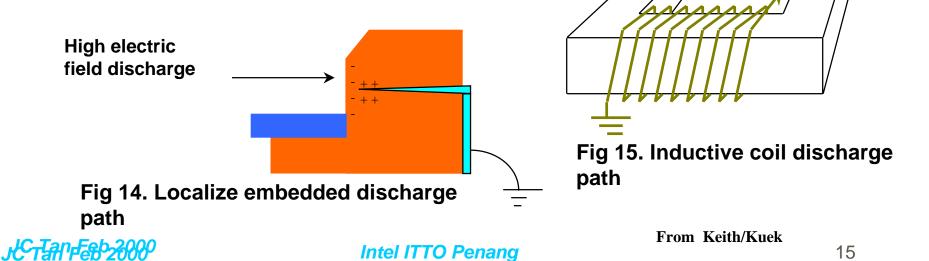

- Localize embedded discharge path to neutralize the charges.

- Enhanced discharge with induction coil

- Apply a conductive material layer

## Summary:

Selection of contactor material and contact technology play a vital role in performance requirements and cost of test contactor design. ESD also has to be taken into consideration during design, and it has become one of the major threat as the trend of CPU design is moving towards low voltage.

## **Conclusion:**

Designer needs to balance between performance requirements and cost. The future test contactor requires high performance, re-usable, long life span, low cost and low in ESD.