Burn-in & Test Socket Workshop 2000

## **Session 2**

## Socket Design

BURN-IN & TEST SOCKET WORKSHOP

#### <u>COPYRIGHT NOTICE</u>

• The papers in this publication comprise the proceedings of the 2000 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, or the Institute of Electrical and Electronic Engineers, Inc.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, proper acknowledgement should be made to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

## **Presentations**

#### "Package Tolerance Of VFQON: Effect On Socket Design"

| David Pfaff | Marc Abelanet |

|-------------|---------------|

| Plastronics | Plastronics   |

#### "Aspect Of Socket Designs And Its Trends"

Lin Pong Goh Intel

#### "Interconnect Solutions For ATE"

Mehdi Attaran Iraj Barbai Oztek Oztek

# Package Tolerance of VFQON: Effect on Socket Design

### 2000 Burn-in and Test Sockets Workshop February 27-29th, 2000

Marc Abelanet and David Pfaff 2601 Texas Drive Irving Texas 75062 972-258-2580; david@locknest.com

## Agenda

- New Package Family

- JEDEC Proposal

- Packaging Industry Versions

- Tolerance Study of JEDEC Proposal

- Effect on Socket Design Optimal Design?

- Conclusion

## **New JEDEC Family**

- Plastic thin fine pitch quad flat no lead package or VFQON

- Industry needs for package

- Light weight

- Small outline

- Excellent electrical characteristics

- Similar to cross

between LCC and LGA packages

## **Packaging Industry Versions**

- Amkor MLF

- ASAT LPCC

- JEDEC MO-208 (example: Fujitsu BCC+)

- JEDEC MO-209 (example: Samsung SON)

- All Similar Types of Packages

- Flat pad leads on peripheral of device

- Leads on bottom side of package only (minimal on side)

- Registration to the socket only on outside of package

- Wide variety of sizes and pitches

- Sizes from 3 to 10 mm

- Pitches of 1, .8, .65, and .5mm

## JEDEC VFQON Package Tolerances

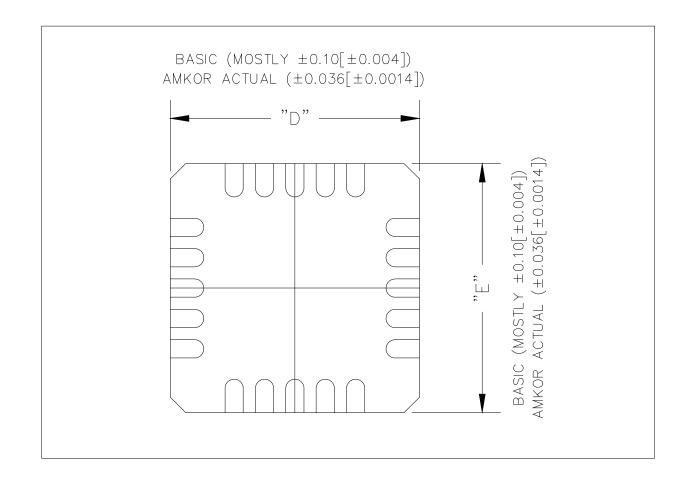

- Analysis of Outside Dimensions

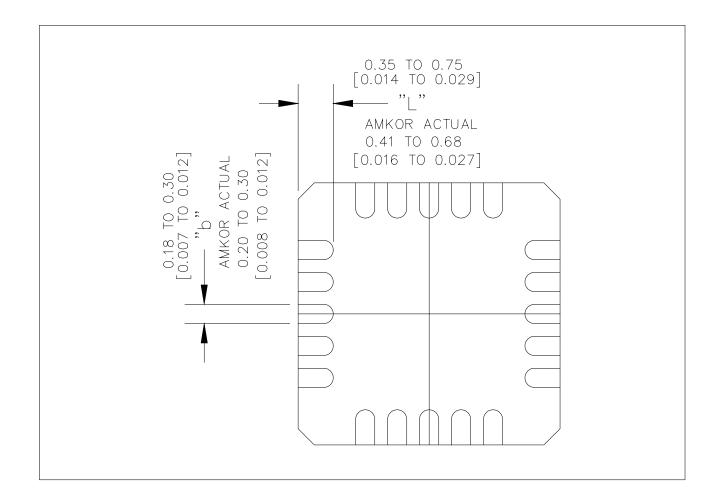

- Analysis of Pad Dimensions

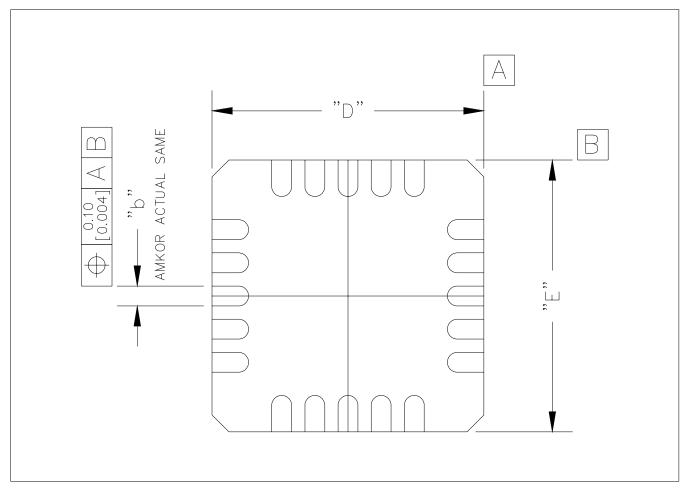

- Locational Tolerances of Pads vs. Body

- Finalized Tolerance Study with all Factors

- Per JEDEC

- Per Amkor MLF

## **Outside Dimensional Tolerances**

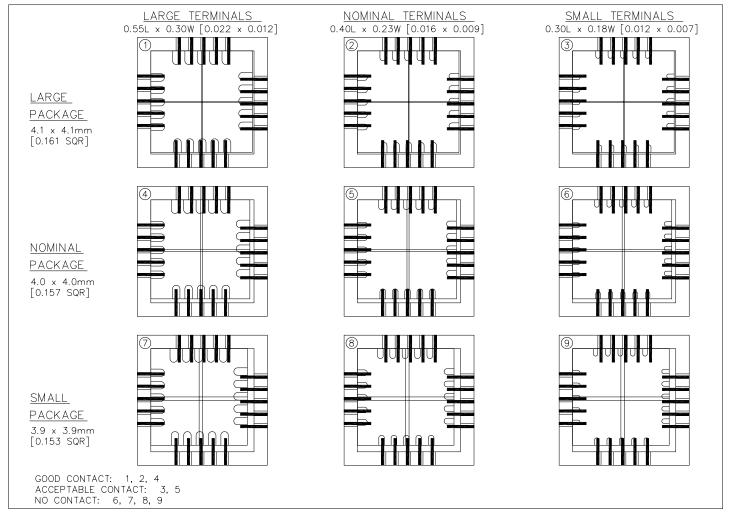

10/11/99BITS Conference February 28th, 2000

## **Pad Dimensional Tolerance**

10/11/99BITS Conference February 28th, 2000

## **Locational Tolerances of Pads**

10/11/99BITS Conference February 28th, 2000

## **Full Tolerance Analysis Per JEDEC**

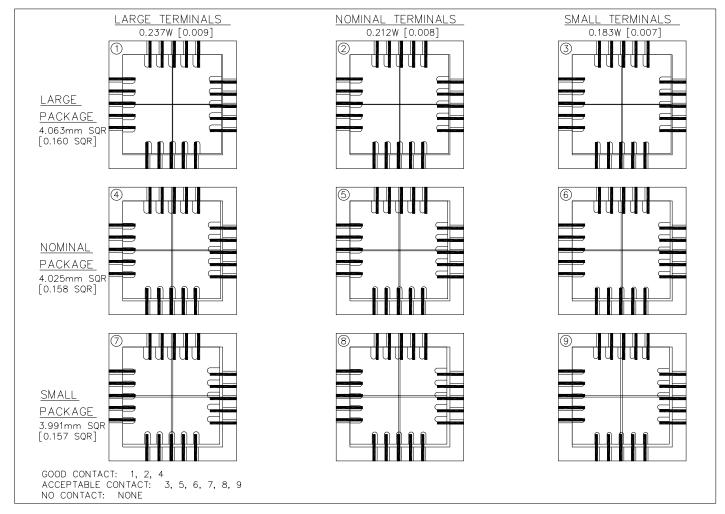

## **Full Tolerance Analysis Per Amkor**

February 28th, 2000

## **Socketing Issues Topics**

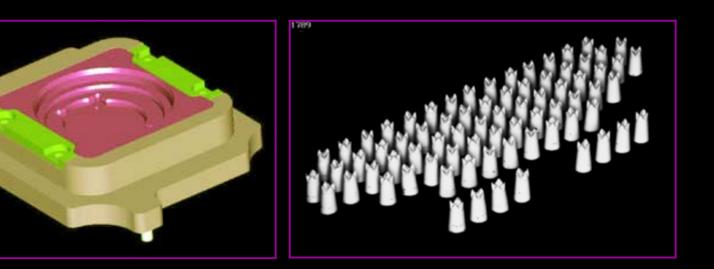

- Electrical Considerations of Contact Element

- Size of Contact

- Ability to Mold Components

- Ability to Assembly Socket

- Inexpensive Method of Providing Sockets for Different Variations of VFQON

- Ability (Difficulty) to Meet Tolerances of Package

## **Electrical Characteristics**

- Package is built for high frequency, telecommunications devices

- Contact for burn-in use, but good electrical specs.

- Inductance ~3nH

- Resistance <30 mOhms

- Surface Compression Mount or Through-Hole

- Size .150"x.150"x.004"

10/11/99BITS Conference

## Mold and Assembly of Socket

- Size of contact .004"

- Molding gate allowance of .006" for slots

- Autoloader machine size tolerance .001"

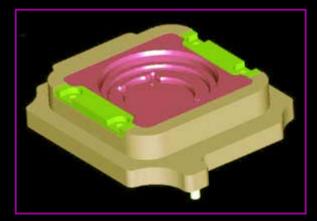

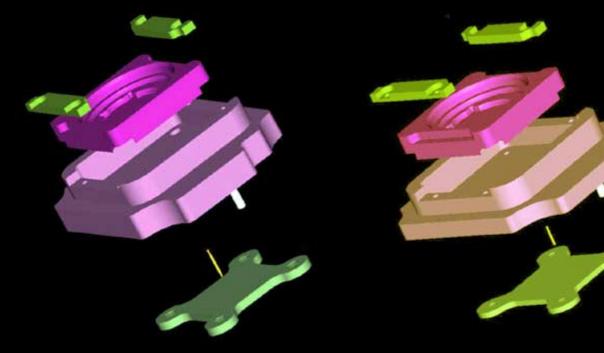

## **Different Size Packages**

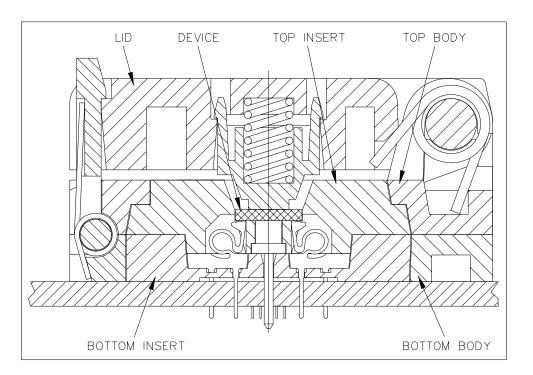

- Must be inexpensive to tool

- One master socket

- Lid with interchangeable pressure plates

- Base

- Two piece modular inserts

- Option of surface mount or through-hole

# Meeting the Tolerance of the Package

- Difficulty to make reliable contact with JEDEC design specifications

- Alignment to the contact pads

- Location of package in plastic guides to be within +/-.001"

- Contact size limited to .004" per force curve considerations

- Contact size also limited to .006" for space between maximum size package terminal

- Tolerances of package critical to build functional socket - mainly OD variation

10/11/99BITS Conference February 28th, 2000

## Conclusion

- Large variety of packages creates requirement for easily adaptable sockets

- Electrical characteristics of new package type create requirement for high-performance contact

- Volume nature of connector creates requirement for low-cost stamped or formed contact

- Tolerance is based on specific packaging house, not wide JEDEC tolerances

BiTS Feb 2000

#### **Aspect of Socket Designs and its Trends**

#### by LP Goh Intel Technology Sdn. Bhd Intel Test Tooling Operation (ITTO) Malaysia

LP Goh Feb 2000

Intel Itto Penang

### Agenda:

#### Introduction

- > Comparison of various types of BIS features

- Current design trend

- Common issues during development

- Future trend

- Conclusion

#### **Objective**

- Elaborate current socket trends from assembly (BIB interface), cost, automation and performance point of view

- > Address common BIS development issues

- Future BIS cost and performance requirement trends

#### Introduction:

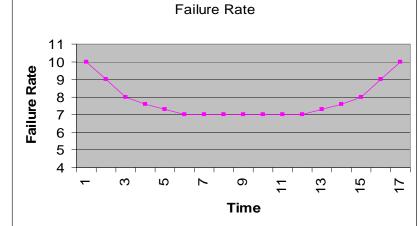

BI: to screen device infant mortality.

BIS: interface hardware between DUT and BIB

Socket's functionality, cost, delivery, maintainability are critical items for product

delivery.

Figure 1: Bath Tub curve

LP Goh Feb 2000

Intel Itto Penang

# Comparison of various types of BIS BITS Feb 2000 features:

#### 1. BIB-interface type of socket.

Cost per unit socket Maintenance BIB interface Through hole Low Difficult (soldered) Reliable

SMT High Easy (screw mounted) Not reliable (BIB warpage)

#### 2. Operation-mode type of socket

Automation Manual operation Dimensional tolerance Actuation Cost per socketing Open top Excellent Not ergonomic Tight (automate) High force Low Clamp shell Poor Recommended Loose (manual) Low force High

### **Current Design trend**

#### 1. Design for BIB assembly process

- A. Through-hole type socket

- >Through-hole type needs to accommodate two challenges:

- Pitch of device lead is getting finer (2.54mm, 1.27mm, 1mm, 0.8mm); as a result, solder bridging (shorted condition between solder tail after wave solder) worsen

- (b) through hole type burn-in socket is not reusable after it has been soldered

- **B. Surface Mount Socket**

- >Challenges faced by surface mount socket:

- (a) high contact-pin-to-pad force induced high warpage on BIB. Extra components are required to minimize warpage.

- (b) Higher cost

BiTS Feb 2000

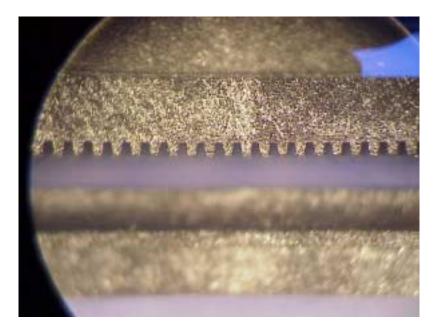

# Impact of solder bridge **Contact pin** Plastic material melted and stick to **Figure 2: Impact of solder bridge** contact pin

LP Goh Feb 2000

Intel Itto Penang

Current Design trend ctd...

#### 2. Design for real estate management and cost

- >higher socket density per board (minimum X & Y)

- higher board density per burn-in oven (minimum Z height), trade off between power, heat sink height and BIS density requirement.

- >increasing number of passive component required per board.

- Sharing mold tool

- re-use socket for close form factor package

Current Design trend ctd...

#### 3. Design for automation

- Tight dimensional tolerance is required for precision alignment between socket and package.

- Open top socket for ease of package loading

- >Long lasting with appropriate material, PES, PEI

- >Actuated type to capture and release package easily

- Robust contact pin design for repetitive process

- >Increasing in pin count, increasing in actuation force

Current Design trend ctd...

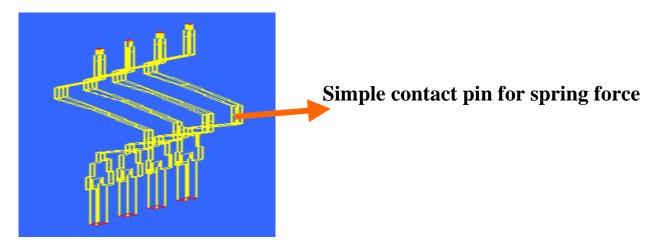

#### 4. Design for performance

- Contact pin to carry high current and low inductance

- High performance heat sink for heat dissipation .

- > Maintain contact pin force while pin count is increasing

**Figure 3: Contact pin design for performance**

LP Goh Feb 2000

Intel Itto Penang

#### **Common Issues during development**

#### >1. Project management/ coordination

•Tool modification lead time impacting project schedule.

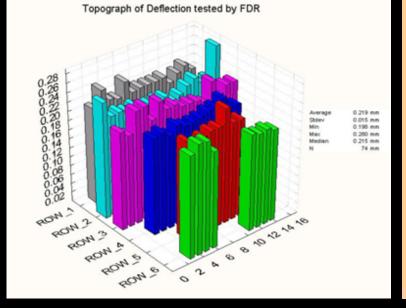

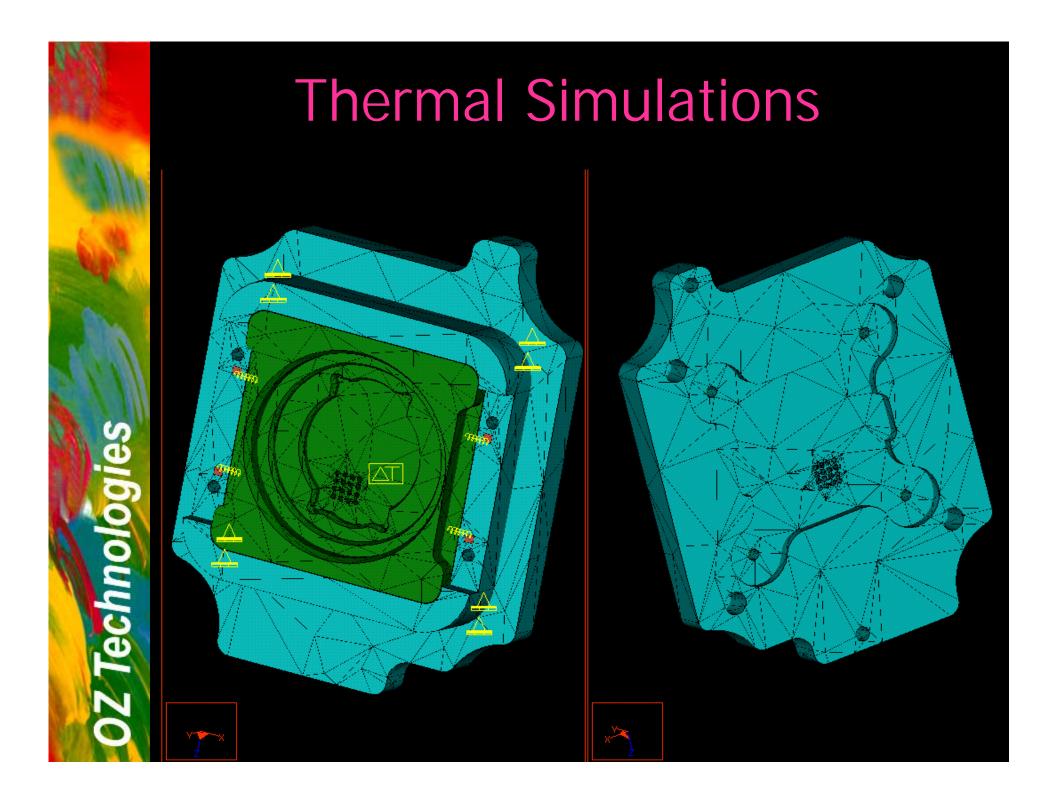

#### >2. Prediction tool capabilities

- Thermal, mechanical and electrical simulation reduces the design modification iteration. Fine tuning on tooling is still required.

- Prototype socket in early discovery work is costly.

Common issues during development ctd.....

#### 3. Component Design

Efficient heat sink requires for high power product occupies invaluable space.

Low inductance contact needed for high frequency testing

Figure 4: Simulation to optimize heat sink geometry

Intel Itto Penang

#### **Future trends**

#### 1. Cost and time to market

- >Replaceable/ reusable socket for next generation burn-in socket.

- Viability of flexible socket tooling

- Concept of test during burn in

#### 2. Socket technology

- Device package is evolving --- smaller in size, more pins. Socket needs to have more pins while maintaining its minimum contact force.

- Socket contact pin performance in high current environment.

#### Conclusion

- Burn-in socket is a critical item to enable product to meet the competitive market needs. The socket design, cost, delivery schedule and volume capacity will come under intense scrutiny in this competitive semiconductor industry.

- The total solution for future burn-in requires re-usable, long lasting, easy to produce, low cost (burn-in per device) and high performance socket. User needs to balance between cost versus performance requirement.

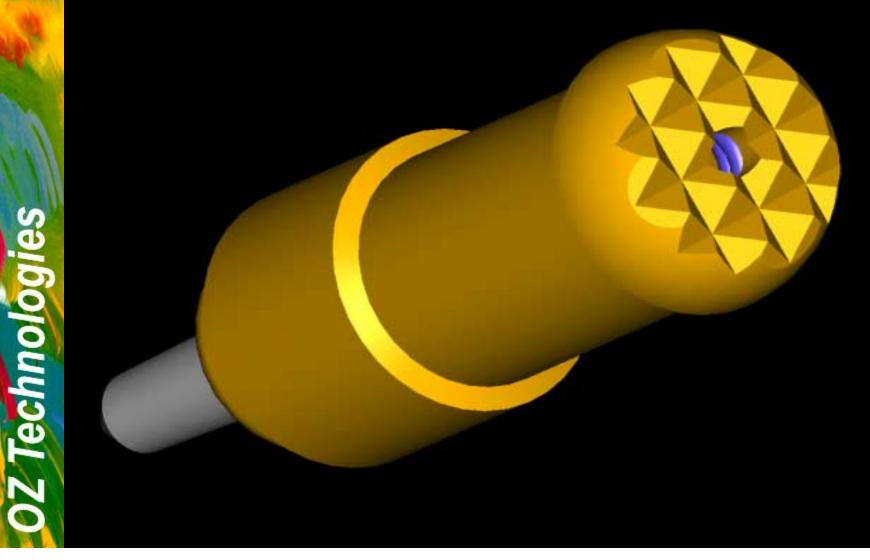

## Interconnect Solutions for ATE

*Iraj Barabi / Mehdi Attaran OZ Technologies Inc.* February 26th 2000

echnolo

## Industry Trends

- Miniaturization

- Reduced Pitch , Increased Pin Count

- Increased Performance Requirements

- Multi-site testing

- Integrated solution

- Speed & flexibility

echnolo

echnolo

## Contactor Design Considerations

- Electrical Performance

- Mechanical Performance

- Dimensional Variations

- Design Reuse\Modularity

- Manual and Automated Test Capability

- Field Serviceable

- Cost Effective

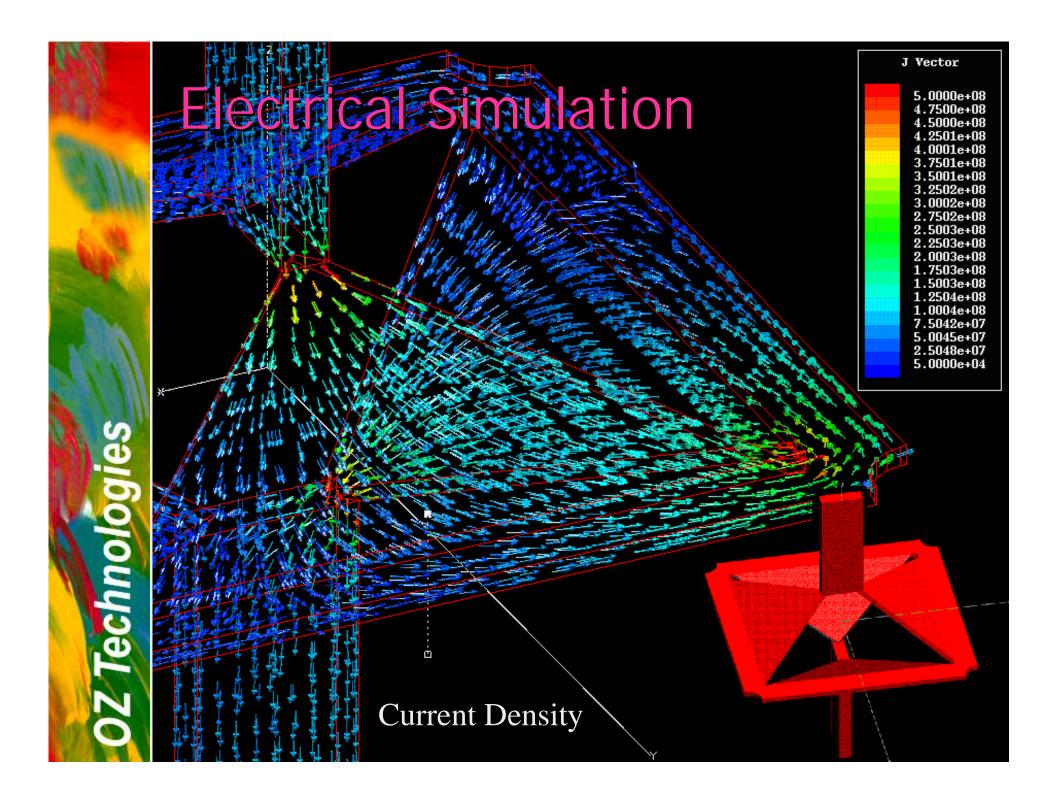

# Electrical Requirements

<u>AC</u>

- < 1nH contact Inductance</p>

- Low cross-talk

- Low capacitance

- Simulation

<u>DC</u>

echnolo

- <40 m Ohm contact Resistance</p>

- Current carrying capacity

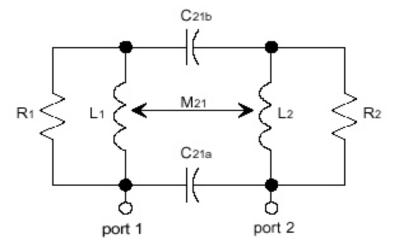

# **Electrical Modeling**

Equivalent Circuit Diagram

| Pins            | L1 & L2<br>(nH) | M <sub>21</sub><br>(nH) | R1 & R2<br>(Ω) | C <sub>21a</sub><br>(pF) | С <sub>21b</sub><br>(pF) |

|-----------------|-----------------|-------------------------|----------------|--------------------------|--------------------------|

| Field adjacent  | 0.58            | 0.12                    | 200            | 0.020                    | 0.025                    |

| Edge adjacent   | 0.65            | 0.13                    | 200            | 0.030                    | 0.030                    |

| Corner adjacent | 0.75            | 0.15                    | 200            | 0.030 <sup>1</sup>       | 0.040 <sup>1</sup>       |

1 estimated values

# **Electrical Modeling**

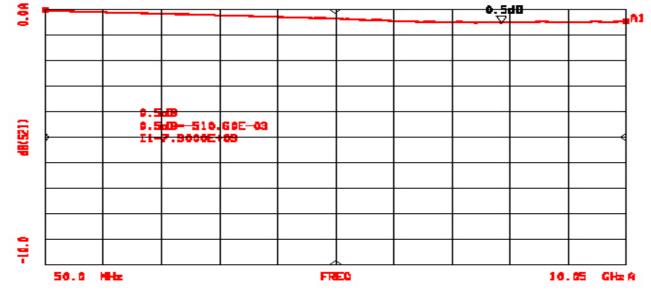

#### Thru measurement, measured vs. simulated response

#### Loop-thru measurement (10 GHz)

es

Technolog

# Mechanical Requirements

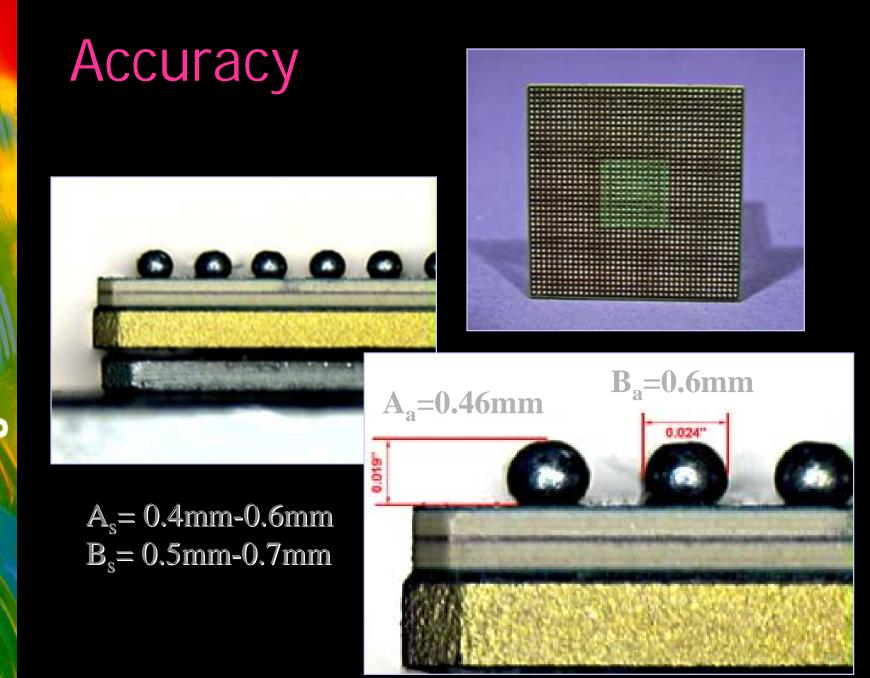

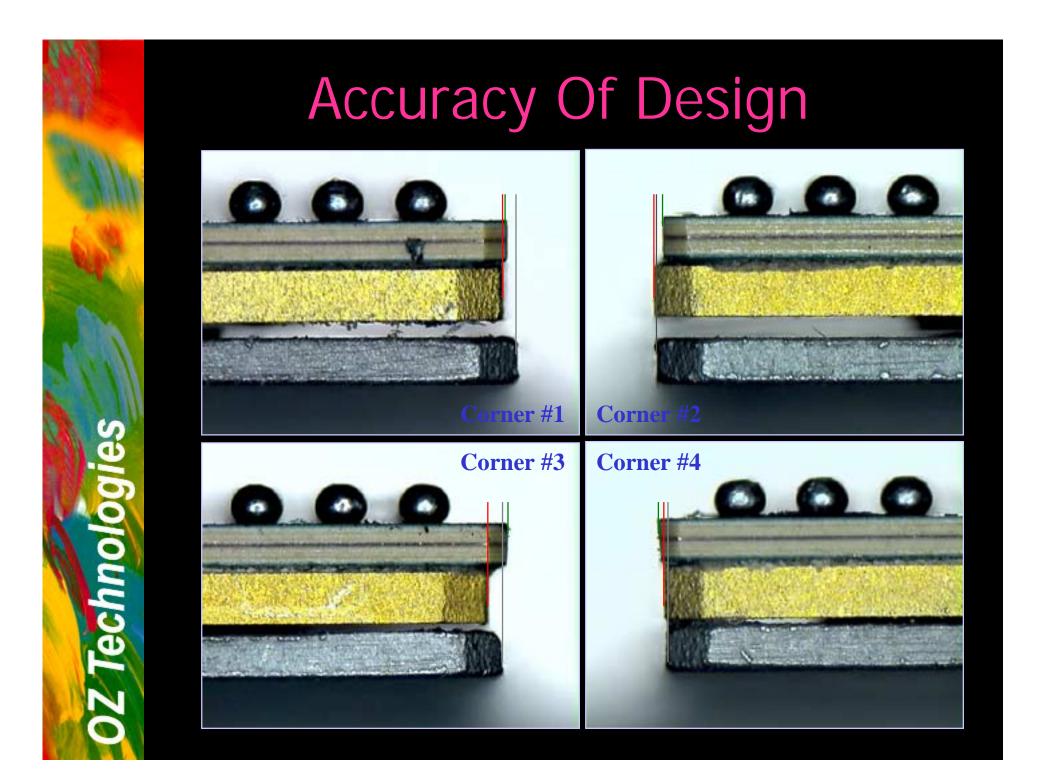

- High level of accuracy

- Simulation & Modeling

- Iarge window of operation

- Modular design

- Iong Life

echnolo

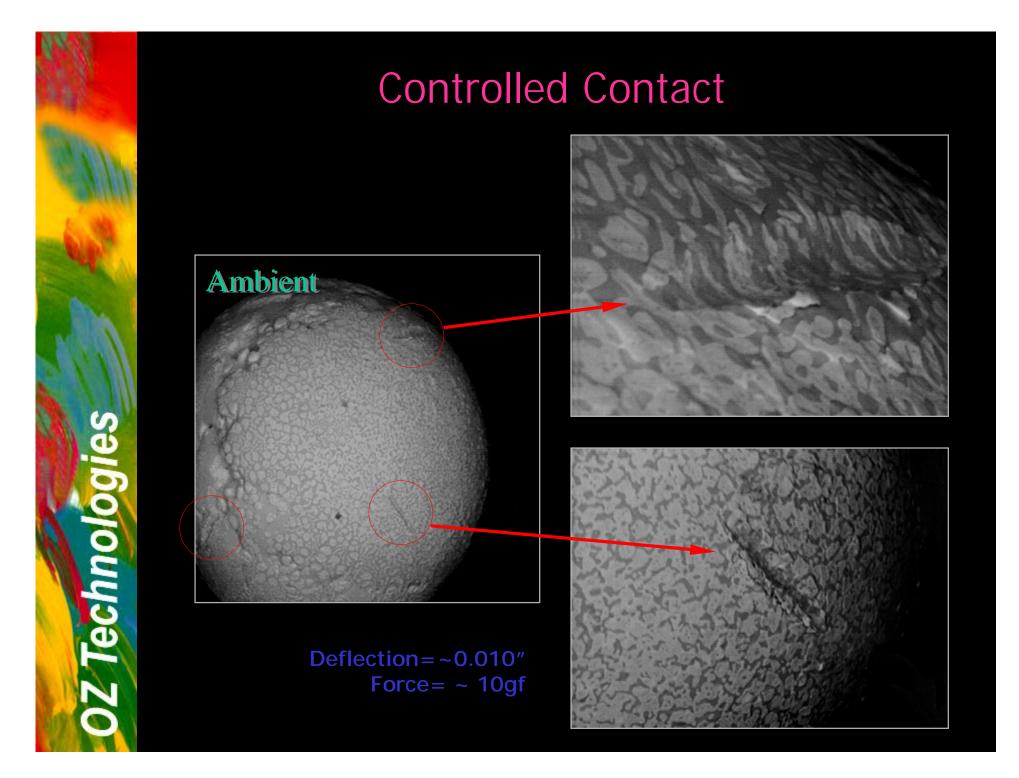

- Reduced mechanical cross-talk

- Controlled contact point

- Thermal consideration

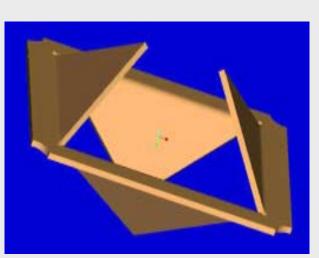

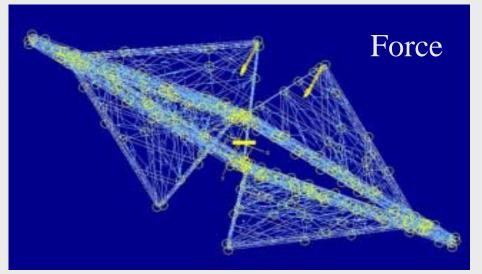

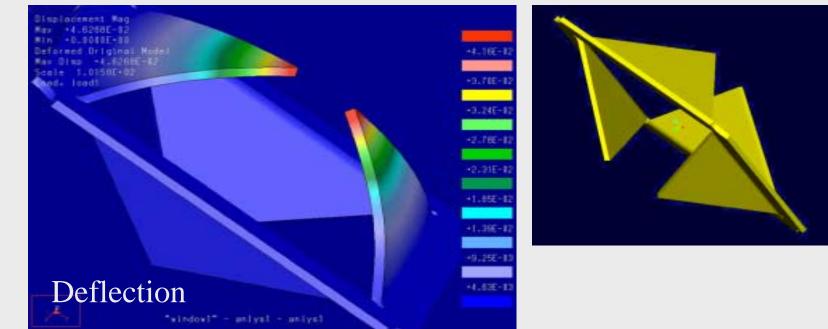

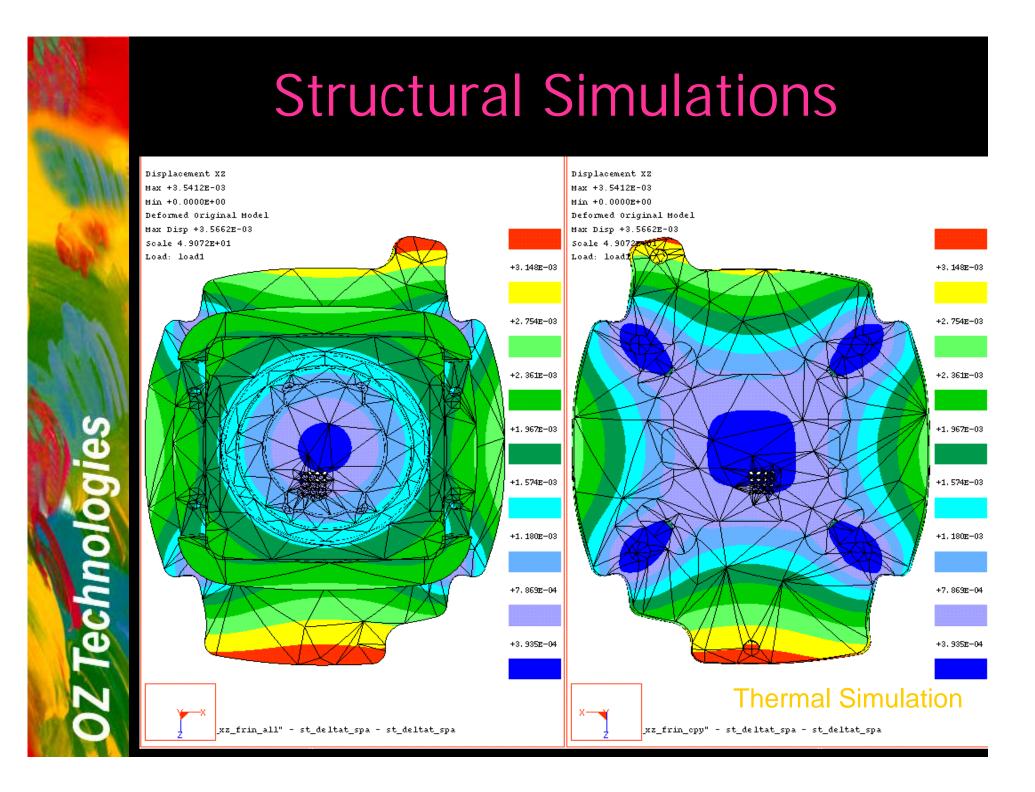

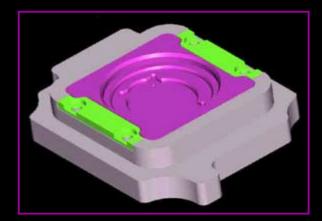

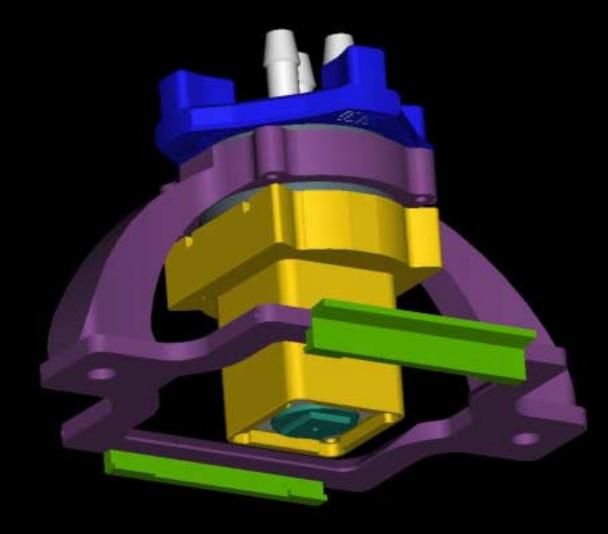

# Mechanical Modeling

## Mechanical Modeling

# Large Window Of Operation

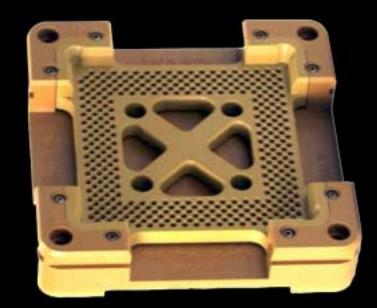

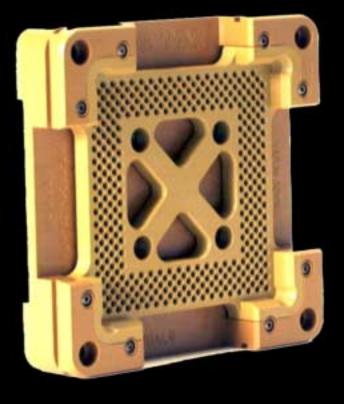

# Modular Design

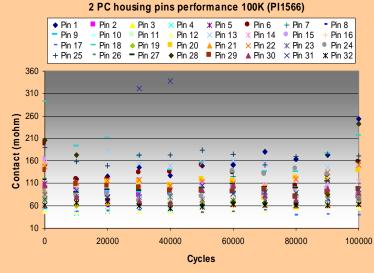

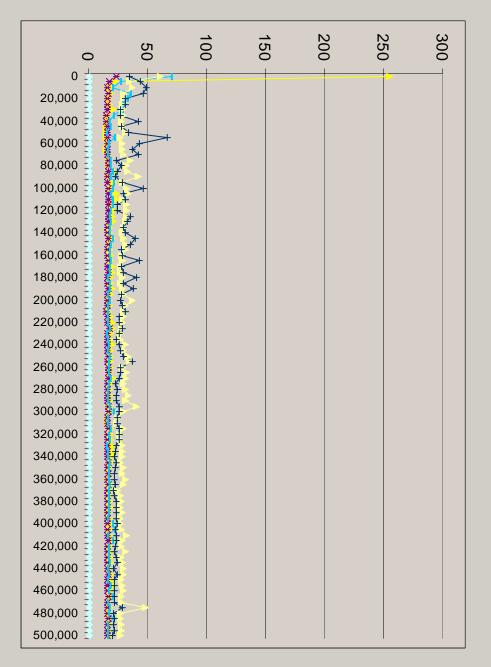

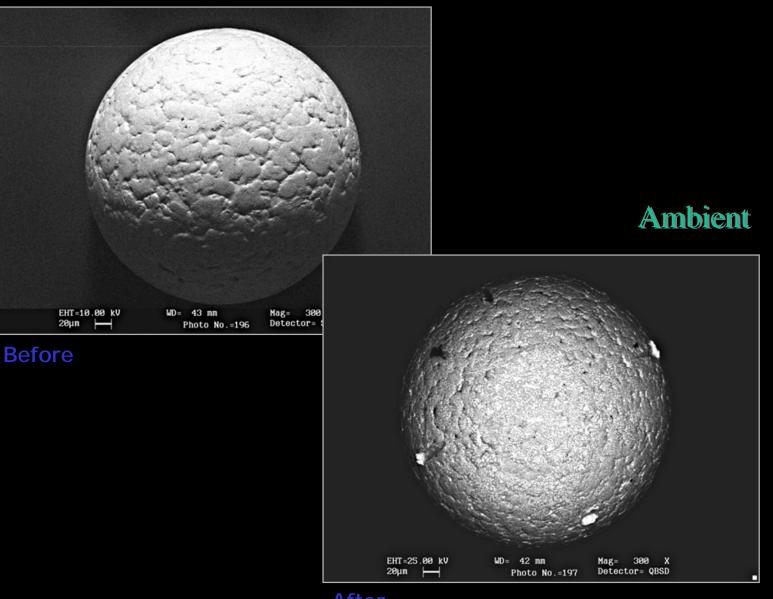

# Life Cycle Testing

### Resistance $m\Omega$

Life cycle vs. Resistance

Number of Insertions

# Technologies

## Mechanical Cross-Talk

## **Controlled** Contact

After

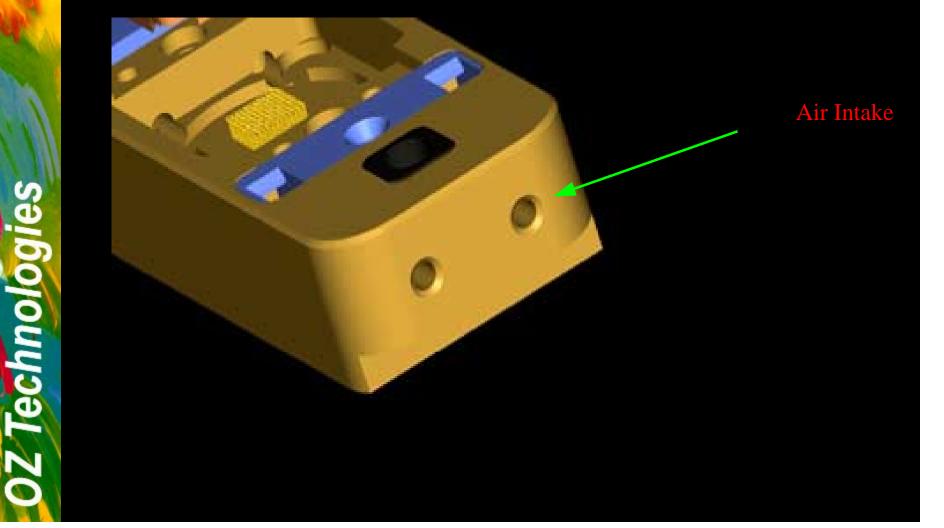

# **Thermal Considerations**

# **Thermal Considerations**

# Conclusion

• Design and validation of ATE test contactors requires a vast array of discipline and technologies.

echnolo

Mechanical, Electrical, Thermal and functional requirements must be optimized in a concurrent and interlinked process to yield necessary performance requirements.